# intel.

## 21256 256K (262,144 x 1) DYNAMIC RAM WITH FAST PAGE MODE

| Symbol           | Parameter            | 21256-08 | Units |

|------------------|----------------------|----------|-------|

| t <sub>RAC</sub> | Access Time from RAS | 80       | ns    |

| t <sub>CAC</sub> | Access Time from CAS | 20       | ns    |

| t <sub>RC</sub>  | Read Cycle Time      | 150      | ns    |

- Page Mode Capability

- CAS-before-RAS Refresh Capability

- RAS-Only and Hidden Refresh Capability

- **TTL Compatible Inputs and Output**

- **Common I/O Using Early Write**

- Single +5V ± 10% Power Supply

- **■** 256 Cycle/4 ms Refresh

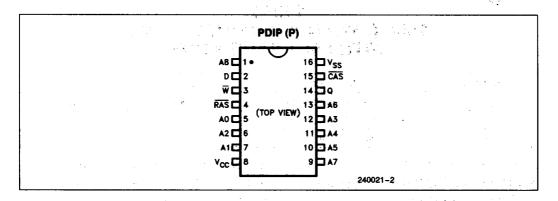

- JEDEC Standard Pinout in PDIP (P)

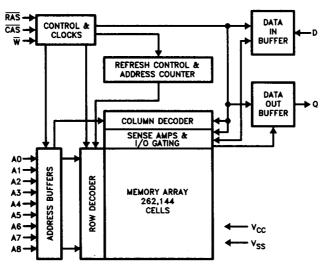

Intel's 21256 is a fully decoded dynamic random access memory organized as 262,144 one-bit words. The design is optimized for high speed, high performance applications such as computer memory, buffer memory, peripheral storage and environments where low power dissipation and compact layout are required.

The 21256 features page mode which allows high speed random access of memory cells within the same row. CAS-before-RAS refresh capability provides on-chip auto refresh as an alternative to RAS-only refresh. Multiplexed row and column address inputs permit the 21256 to be housed in a JEDEC standard 16-pin DIP.

Clock timing requirements are noncritical, and power supply tolerance is very wide. All inputs and output are TTL compatible.

Figure 1. Functional Block Diagram

#### Pin Names

| A <sub>0</sub> -A <sub>8</sub> | Address Input         |

|--------------------------------|-----------------------|

| D                              | Data In               |

| Q                              | Data Out              |

| ₩                              | Read/Write Input      |

| RAS                            | Row Address Strobe    |

| CAS                            | Column Address Strobe |

| Vcc                            | Power (+5V)           |

| Vss                            | Ground                |

## ABSOLUTE MAXIMUM RATINGS\*

| Voltage on Any Pin Relative to V <sub>SS</sub> V <sub>OUT</sub> -1.0V to +7.0V |

|--------------------------------------------------------------------------------|

| Voltage on V <sub>CC</sub> Supply<br>Relative to V <sub>SS</sub> 1.0V to +7.0V |

| Storage Temperature55°C to +125°C                                              |

| Power Dissipation1.0W                                                          |

| Short Circuit Output Current 50 mA                                             |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS Voltages referenced to V<sub>SS</sub>, T<sub>A</sub> = 0 to 70°C

| Symbol          | Parameter          | Min | Тур | Max                | Units |

|-----------------|--------------------|-----|-----|--------------------|-------|

| V <sub>CC</sub> | Supply Voltage     | 4.5 | 5.0 | 5.5                | ٧     |

| V <sub>SS</sub> | Ground             | 0   | 0   | 0                  | ٧     |

| VIH             | Input High Voltage | 2.4 |     | V <sub>CC</sub> +1 | ٧     |

| V <sub>IL</sub> | Input Low Voltage  | -1  |     | 0.8                | V     |

#### DC AND OPERATING CHARACTERISTICS

Recommended operating conditions unless otherwise noted.

| Symbol           | Parameter                       |          | Min | Max | Units | Test Condition                                                                                                |

|------------------|---------------------------------|----------|-----|-----|-------|---------------------------------------------------------------------------------------------------------------|

| ICC1             | Operating Current*              | 21256-08 |     | 60  | mA    | (RAS and CAS<br>cycling @ t <sub>RC</sub> = min.)                                                             |

| I <sub>CC2</sub> | Standby Current                 | 21256-08 |     | 2.0 | mA    | (RAS = CAS = VIH)                                                                                             |

| ICC3             | RAS-Only Refresh Current*       | 21256-08 |     | 60  | mA    | (CAS = V <sub>IH</sub> , RAS<br>cycling @ t <sub>RC</sub> = min.)                                             |

| I <sub>CC4</sub> | Page Mode Current*              | 21256-08 |     | 40  | mA    | (RAS = V <sub>IL</sub> , CAS cycling;<br>t <sub>PC</sub> = min.)                                              |

| I <sub>CC5</sub> | CAS-before-RAS Refresh Current* | 21256-08 |     | 55  | mA    | (RAS cycling @ t <sub>RC</sub> = min.)                                                                        |

| I <sub>CC6</sub> | Standby Current                 |          |     | 1.0 | mA    | $(RAS = \overline{CAS} = V_{CC} - 0.2V)$                                                                      |

| I <sub>IL</sub>  | Input Leakage Current           |          | -10 | 10  | μА    | (Any input $0 \le V_{IN} \le 5.5V$ , $V_{CC} = 5.5V$ , $V_{SS} = 0V$ , All other pins not under test $= 0$ .) |

| loL              | Output Leakage Current          |          | -10 | 10  | μΑ    | (Data out is disabled,<br>$0V \le V_{OUT} \le 5.5V$ ,<br>$V_{CC} = 5.5V$ , $V_{SS} = 0V$ )                    |

#### \*NOTE:

ICC1, ICC3, ICC4 and ICC5 are dependent on output loading and cycle rates. Specified values are obtained with the output open. ICC is specified as average current.

#### DC AND OPERATING CHARACTERISTICS

Recommended operating conditions unless otherwise noted. (Continued)

| Symbol          | Parameter                 | Min | Max | Units | Test Condition            |

|-----------------|---------------------------|-----|-----|-------|---------------------------|

| V <sub>OH</sub> | Output High Voltage Level | 2.4 |     | ٧     | $(l_{OH} = 5 \text{ mA})$ |

| VOL             | Output Low Voltage Level  |     | 0.4 | ٧     | $(I_{OL} = 4.2  mA)$      |

## CAPACITANCE TA = 25°C

| Symbol           | Parameter                                              | Min    | Max | Units |

|------------------|--------------------------------------------------------|--------|-----|-------|

| C <sub>IN1</sub> | Input Capacitance (A <sub>0</sub> -A <sub>8</sub> , D) | , to 1 | 5   | pF    |

| C <sub>IN2</sub> | Input Capacitance (RAS, CAS, W)                        |        | 8   | pF    |

| C <sub>OUT</sub> | Output Capacitance (Q)                                 |        | 7   | pF    |

## AC CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 5.0V $\pm$ 10%. See Notes 1, 2)

| Symbol           | Parameter                                           | · 212 | :56-08 | Units | Notes  |

|------------------|-----------------------------------------------------|-------|--------|-------|--------|

| •,               | i arameter                                          | Min   | Max    |       | 110103 |

| t <sub>RC</sub>  | Random Read or<br>Write Cycle Time                  | 150   |        | ns    |        |

| tRWC             | Read-Modify-Write Cycle Time                        | 175   |        | ns    |        |

| t <sub>RAC</sub> | Access Time from RAS                                |       | 80     | ns    | 3,4,11 |

| t <sub>CAC</sub> | Access Time from CAS                                |       | 30     | ns    | 3,4,5  |

| t <sub>AA</sub>  | Column Address Access Time                          |       | 40     | ns    | 3,10   |

| tclz             | CAS to Output in Low-Z                              | 5     |        | ns    | 3      |

| t <sub>OFF</sub> | Output Buffer Turn-Off Delay                        | 0     | 25     | ns    | 7      |

| t <sub>T</sub>   | Transition Time (Rise and Fall)                     | 3     | 50     | ns    | . 2    |

| t <sub>RP</sub>  | RAS Precharge Time                                  | 75    |        | ns    |        |

| tRAS             | RAS Pulse Width                                     | 80    | 10,000 | ns    |        |

| t <sub>RSH</sub> | RAS Hold Time                                       | 30    |        | ns    |        |

| t <sub>CPN</sub> | CAS Precharge Time<br>(All Cycles except Page Mode) | 15    |        | ns    |        |

| tCAS             | CAS Pulse Width                                     | 30    | 10,000 | ns    |        |

| t <sub>CSH</sub> | CAS Hold Time                                       | 80    |        | ns    |        |

| tRCD             | RAS to CAS Delay Time                               | 25    | 60     | ns    | 4      |

| t <sub>RAD</sub> | RAS to Column Address<br>Delay Time                 | 20    | 40     | ns    | 11     |

| tCRP             | CAS to RAS Precharge Time<br>(RAS Only Refresh)     | 15    |        | ns    |        |

| tasr             | Row Address Setup Time                              | 0     |        | ns    |        |

AC CHARACTERISTICS (0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, V<sub>CC</sub> = 5.0V  $\pm$ 10%. See Notes 1, 2) (Continued)

| Symbol           | Parameter                                     | 212 | 56-08 | Units | Notes  |

|------------------|-----------------------------------------------|-----|-------|-------|--------|

|                  | T dramotor                                    | Min | Max   |       | 110101 |

| t <sub>RAH</sub> | Row Address Hold Time                         | 15  |       | ns    |        |

| tasc             | Column Address Setup Time                     | 0   |       | ns    |        |

| t <sub>CAH</sub> | Column Address Hold Time                      | 20  |       | ns    |        |

| t <sub>AR</sub>  | Column Address Hold Time<br>Referenced to RAS | 65  |       | ns    | 6      |

| t <sub>RAL</sub> | Column Address to RAS<br>Lead Time            | 40  |       | ns    |        |

| t <sub>RCS</sub> | Read Command Setup Time                       | 0   |       | ns    |        |

| t <sub>RCH</sub> | Read Command Hold Time<br>Referenced to CAS   | 5   |       | ns    | 9      |

| t <sub>RRH</sub> | Read Command Hold Time<br>Referenced to RAS   | 5   |       | ns    | 9      |

| twcs             | Write Command Setup Time                      | 0   |       | ns    | 8      |

| twch             | Write Command Hold Time                       | 15  |       | ns    |        |

| t <sub>WP</sub>  | Write Command Pulse Width                     | 15  |       | ns    |        |

| t <sub>RWL</sub> | Write Command to RAS Lead Time                | 30  |       | ns    |        |

| tcwL             | Write Command to CAS Lead Time                | 30  |       | ns    |        |

| t <sub>DS</sub>  | Data-In Setup Time                            | 0   |       | ns    | 10     |

| t <sub>DH</sub>  | Data-In Hold Time                             | 15  |       | ns    | 10     |

| tcwp             | CAS to Write Enable Delay                     | 25  |       | ns    | 8      |

| t <sub>RWD</sub> | RAS to Write Enable Delay                     | 80  |       | ns    | 8      |

| t <sub>AWD</sub> | Column Address to W Delay Time                | 40  |       | ns    | 8      |

| twcn             | Write Command Hold Time<br>Referenced to RAS  | 60  |       | ns    | 6      |

| t <sub>DHR</sub> | Data-in Hold Time<br>Referenced to RAS        | 60  |       | ns    | 6      |

| t <sub>REF</sub> | Refresh Period (256 Cycles)                   |     | 4     | ms    |        |

| CAS-BEFC         | RE-RAS REFRESH                                |     |       |       |        |

| tcsr             | CAS Setup Time<br>(CAS-before-RAS Refresh)    | 10  |       | ns    |        |

| tCHR             | CAS Hold Time<br>(CAS-before-RAS Refresh)     | 25  |       | ns    |        |

| t <sub>CPT</sub> | Refresh Counter Test CAS Precharge Time       | 50  |       | ns    |        |

| t <sub>RPC</sub> | RAS Precharge to CAS Active Time              | 10  |       | ns    |        |

| PAGE MOI         | DE                                            |     | -     |       |        |

| t <sub>PC</sub>  | Page Mode Cycle Time                          | 55  |       | ns    |        |

| t <sub>CP</sub>  | CAS Precharge Time<br>(Page Mode Only)        | 15  |       | ns    |        |

|                  |                                               | L   | 4     | 1     |        |

## intها.

## AC CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 5.0V $\pm$ 10%. See Notes 1, 2) (Continued)

| Symbol            | Parameter                           | 212 | 256-08 | Units | Notes |

|-------------------|-------------------------------------|-----|--------|-------|-------|

|                   | i di diliotoi                       | Min | Max    |       |       |

| PAGE MOD          | E (Continued)                       |     |        |       |       |

| t <sub>CPA</sub>  | Access Time from CAS Precharge      |     | 50     | ns    | 3     |

| t <sub>PRWC</sub> | Fast Page Mode<br>Read-Modify-Write | 85  |        | ns    |       |

| tRASP             | RAS Pulse Width (Fast Page Mode)    | 80  | 10,000 | ns .  |       |

#### NOTES:

- 1. An initial pause of 200  $\mu s$  is required after power-up followed by any 8 RAS cycles before proper device operation is

- 2. V<sub>IH</sub>(min) and V<sub>II</sub> (max) are reference levels for measuring timing of input signals. Transition times are measured between VIH(min) and VIL (max) and are assumed to be 5 ns for all inputs.

3. Measured with a load equivalent to 2 TTL loads and 100 pF.

4. Operation within the T<sub>RCD</sub>(max) limit ensures that T<sub>RAC</sub>(max) can be met, t<sub>RCD</sub>(max) is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

5. Assumes that  $t_{RCD} \ge t_{RCD}(max)$ .

- 6. t<sub>AR</sub>, t<sub>WCR</sub>, t<sub>DHR</sub> are referenced to t<sub>RAD(max)</sub>.

7. This parameter defines the time at which the output achieves the open circuit condition and is not referenced to V<sub>OH</sub> or VOL.

- 8. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are non-restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If twcs ≥ twcs(min) the cycle is an early write cycle and the data out pin will remain high impedance for the duration of the cycle. If t<sub>CWD</sub> ≥ t<sub>CWD(min)</sub>, t<sub>RWD</sub> ≥ t<sub>RWD(min)</sub> and t<sub>AWD</sub> ≥ t<sub>AWD(min)</sub>, then the cycle is a read-write cycle and the data out will contain the data read from the selected address. If neither of the above conditions are satisfied, the condition of the data out is indeterminate.

9. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- 10. These parameters are referenced to the CAS leading edge in early write cycles and to the W leading edge in read-write

- 11. Operation within the t<sub>RAD(max)</sub> limit insures that t<sub>RAC(max)</sub> can be met. t<sub>RAD(max)</sub> is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD(max)</sub> limit, then access time is controlled by t<sub>AA</sub>.

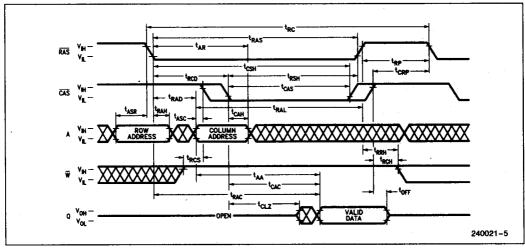

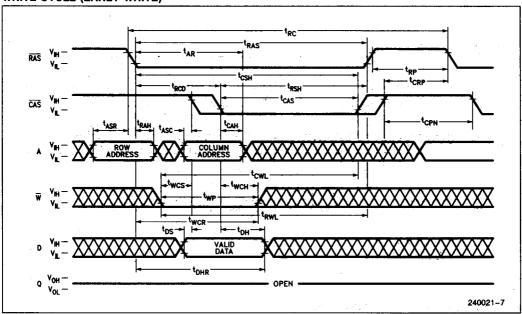

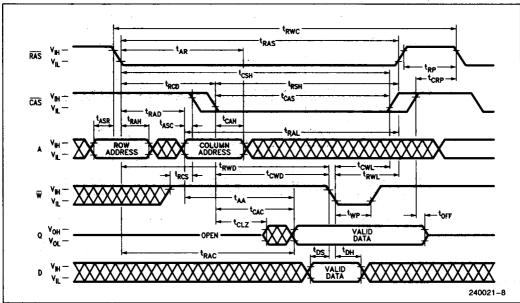

#### TIMING DIAGRAMS

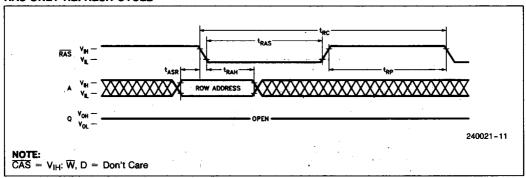

#### **READ CYCLE**

XXXI Don't Care

#### WRITE CYCLE (EARLY WRITE)

#### READ-WRITE/READ-MODIFY-WRITE CYCLE

Don't Care

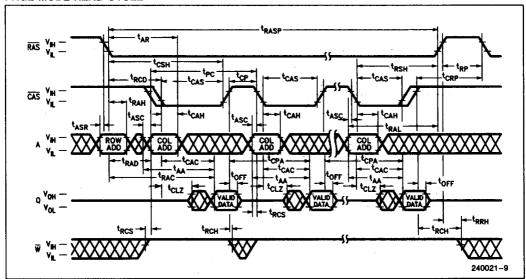

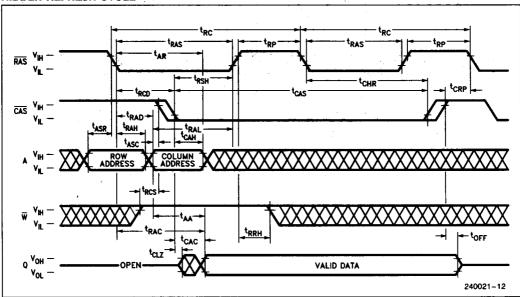

#### PAGE MODE READ CYCLE

#### PAGE MODE WRITE CYCLE (EARLY WRITE)

Don't Care

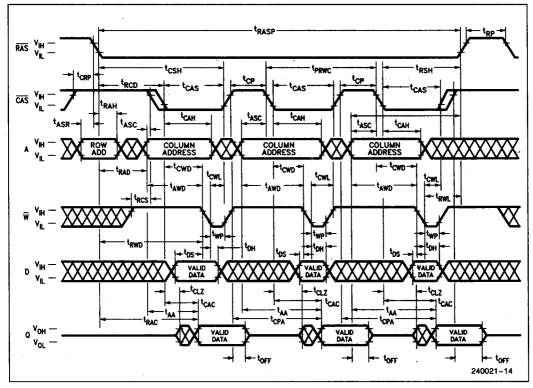

#### PAGE MODE READ-WRITE CYCLE

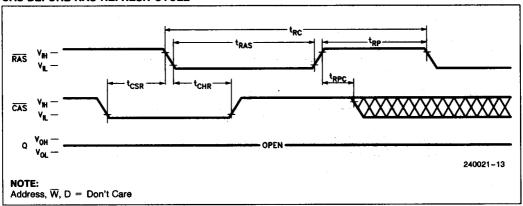

#### **RAS-ONLY REFRESH CYCLE**

#### HIDDEN REFRESH CYCLE

Don't Care

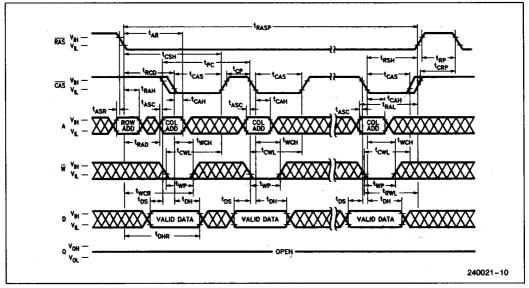

#### CAS-BEFORE-RAS REFRESH CYCLE

Don't Care

## intel.

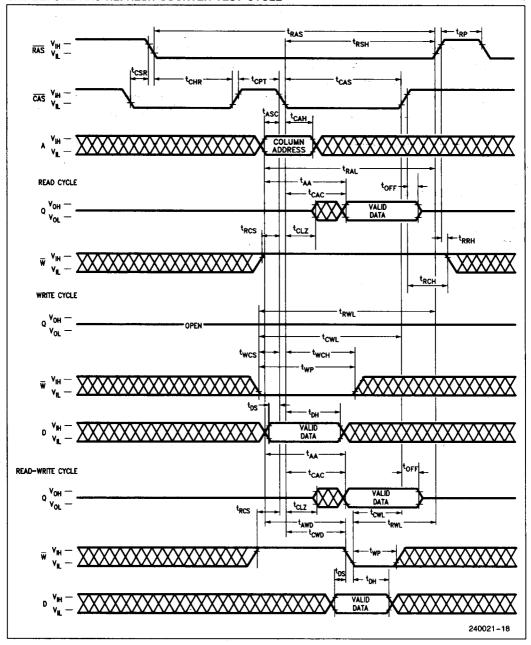

#### TIMING DIAGRAMS (Continued)

#### **CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE**

240021\_6

#### **DEVICE OPERATION**

The 21256 contains 262,144 memory locations. Eighteen address bits are required to address a particular memory location. Since the 21256 has only 9 address input pins, time multiplexed addressing is used to input 9 row and 9 column addresses. The multiplexing is controlled by the timing relationship between the row address strobe (RAS), the column address strobe (CAS) and the valid address inputs.

Operation of the 21256 begins by strobing in a valid row address with RAS while CAS remains high. Then the address on the 9 address input pins is changed from a row address to a column address and is strobed in by CAS. This is the beginning of any 21256 cycle in which a memory location is accessed. The specific type of cycle is determined by the state of the write enable pin and various timing relationships. The cycle is terminated when both RAS and CAS have returned to the high state. Another cycle can be initiated after RAS remains high long enough to satisfy the RAS precharge time (t<sub>RP</sub>) requirement.

#### RAS and CAS Timing

The minimum RAS and CAS pulse widths are specified by t<sub>RAS</sub>(min) and t<sub>CAS</sub>(min) respectively. These minimum pulse widths must be satisfied for proper device operation and data integrity. Once a cycle is initiated by bringing RAS low, it must not be aborted prior to satisfying the minimum RAS and CAS pulse widths. In addition, a new cycle must not begin until the minimum RAS precharge time, t<sub>RP</sub>, has been satisfied. Once a cycle begins, internal clocks and other circuits within the 21256 begin a complex sequence of events. If the sequence is broken by violating minimum timing requirements, loss of data integrity can occur.

#### Read

A read cycle is achieved by maintaining the write enable input  $(\overline{W})$  high during a  $\overline{RAS}/\overline{CAS}$  cycle. The output of the 21256 remains in the Hi-Z state until valid data appears at the output. If  $\overline{CAS}$  goes low before  $t_{RCD}(max)$ , the access time to valid data is specified by  $t_{RAC}$ . If  $\overline{CAS}$  goes low after  $t_{RCD}(max)$ , the access time is measured from  $\overline{CAS}$  and is specified by  $t_{CAC}$ . In order to achieve the minimum access time,  $t_{RAC}(min)$ , it is necessary to bring  $\overline{CAS}$  low before  $t_{RCD}(max)$ .

#### Write

The 21256 can perform early write, late write and read-modify-write cycles. The difference between these cycles is in the state of data-out and is determined by the timing relationship between  $\overline{W}$  and  $\overline{CAS}$ . In any type of write cycle, data-in must be valid at or before the falling edge of  $\overline{W}$  or  $\overline{CAS}$ , whichever is later.

Early Write: An early write cycle is performed by bringing W low before CAS. The data at the data input pin (D) is written into the addressed memory cell. Throughout the early write cycle the output remains in the Hi-Z state. This cycle is good for common I/O applications because the data-in and data-out pins may be tied together without bus contention.

Read-Modify-Write: In this cycle, valid data from the addressed cell appears at the output before and during the time that data is being written into the same cell location. This cycle is achieved by bringing W low after CAS and meeting the data sheet read-modify-write cycle timing requirements. This cycle requires using a separate I/O to avoid bus contention.

Late Write: If  $\overline{W}$  is brought low after  $\overline{CAS}$ , a late write cycle will occur. The late write cycle is very similar to the read-modify-write cycle except that the timing parameters,  $t_{RWD}$  and  $t_{CWD}$ , are not necessarily met. The state of data-out is indeterminate since the output could be either Hi-Z or contain data depending on the timing conditions. This cycle requires a separate I/O to avoid bus contention.

#### **Data Output**

The 21256 has a tri-state output buffer which is controlled by  $\overline{\text{CAS}}$  (and  $\overline{\text{W}}$  for early write). Whenever  $\overline{\text{CAS}}$  is high (V<sub>IH</sub>) the output is in the high impedance (Hi-Z) state. In any cycle in which valid data appears at the output, the output first remains in the Hi-Z state until the data is valid and then the valid data appears at the output. The valid data remains at the output until  $\overline{\text{CAS}}$  returns high. This is true even if a new  $\overline{\text{RAS}}$  cycle occurs (as in hidden refresh). Each of the 21256 operating cycles is listed below after the corresponding output state produced by the cycle

Valid Output Data: Read, Read-Modify-Write, Hidden Refresh, Page Mode Read, Page Mode Read-Modify-Write.

Hi-Z Output State: Early Write, RAS-only Refresh, Page Mode Write, CAS-before-RAS Refresh, CAS-only cycle.

Indeterminate Output State: Delayed Write

#### Refresh

The data in the 21256 is stored on a tiny capacitor within each memory cell. Due to leakage, the data will leak off after a period of time. To maintain data integrity it is necessary to refresh each of the rows every 4 ms. There are several ways to accomplish this.

RAS-Only Refresh: This is the most common method for performing refresh. It is performed by strobing in a row address with RAS while CAS remains high.

CAS-before-RAS Refresh: The 21256 has CAS-before-RAS on-chip refreshing capability that eliminates the need for external refresh addresses. If CAS is held low for the specified setup time (t<sub>CSR</sub>) before RAS goes low, the on-chip refresh circuitry is enabled. An internal refresh operation automatically occurs and the on-chip refresh address counter is internally incremented in preparation for the next CAS-before-RAS refresh cycle.

Hidden Refresh: A hidden refresh cycle may be performed while maintaining the latest valid data at the output by extending the CAS active time and cycling RAS. The 21256 hidden refresh cycle is actually a CAS-before-RAS refresh cycle within an extended read cycle. The refresh row address is provided by the on-chip refresh address counter. This eliminates the need for the external row address that is required in hidden refresh cycles by DRAMs that do not have CAS-before-RAS refresh capability.

Other Refresh Methods: It is also possible to refresh the 21256 by using read, write or read-modify-write cycles. Whenever a row is accessed, all the cells in that row are automatically refreshed. There are certain applications in which it might be advantageous to perform refresh in this manner but in general RAS-only or CAS-before-RAS refresh is the preferred method.

#### Page Mode

The 21256 has page mode capability. Page mode memory cycles provide faster access and lower power dissipation than normal memory cycles. In page mode, it is possible to perform read, write or

read-modify-cycles. As long as the applicable timing requirements are observed, it is possible to mix these cycles in any order. A page mode cycle begins with a normal cycle. While RAS is kept low to maintain the row address, CAS is cycled to strobe in additional column addresses. This eliminates the time required to set up and strobe sequential row addresses for the same page.

# CAS-before-RAS Refresh Counter Test Cycle

A special timing sequence using the CAS-before-RAS counter test cycle provides a convenient method of verifying the functionality of the CAS-before-RAS refresh activated circuitry.

After the CAS-before-RAS refresh operation, if CAS goes high and then low again while RAS is held low, the read and write operations are enabled.

This is shown in the CAS-before-RAS counter test cycle timing diagram. A memory cell can be addressed with 9 row address bits and 9 column address bits defined as follows:

Row Address—Bits A0 through A7 are supplied by the on-chip refresh counter. The A8 bit is set high internally.

Column Address—Bits A0 through A8 are strobedin by the falling edge of CAS as in a normal memory cycle.

# Suggested CAS-before-RAS Counter Test Procedure

The CAS-before-RAS refresh counter test cycle timing is used in each of the following steps:

- Initialize the internal refresh counter by performing 8 cycles.

- Write a test pattern of "lows" into the memory cells at a single column address and 256 row addresses. (The row addresses are supplied by the on-chip refresh counter.)

- Using read-modify-write cycles, read the "lows" written during step 2 and write "highs" into the same memory locations. Perform this step 256 times so that highs are written into the 256 memory cells.

- 4. Read the "highs" written during step 3.

- Complement the test pattern and repeat steps 2, 3 and 4.

#### **Power-Up**

If  $\overline{\text{RAS}} = \text{V}_{\text{SS}}$  during power-up, the 21256 could begin an active cycle. This condition results in higher than necessary current demands from the power supply during power-up. It is recommended that  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  track with  $\text{V}_{\text{CC}}$  during power-up or be held at a valid  $\text{V}_{\text{H}}$  in order to minimize the power-up current.

An initial pause of 100  $\mu s$  is required after power-up followed by 8 initialization cycles before proper device operation is assured. 8 initialization cycles are also required after any 4 ms period in which there are no RAS cycles. An initialization cycle is any cycle in which RAS is cycled.

#### **Termination**

The lines from the TTL driver circuits to the 21256 inputs act like unterminated transmission lines resulting in significant positive and negative overshoots at the inputs. To minimize overshoot it is advisable to terminate the input lines and to keep them as short as possible. Although either series or parallel termination may be used, series termination is generally recommended since it is simple and draws no additional power. It consists of a resistor in series with the input line placed close to the 21256 input pin. The optimum value depends on the board layout. It must be determined experimentally and is usually in the range of  $20\Omega$  to  $40\Omega$ .

#### **Board Layout**

It is important to lay out the power and ground lines on memory boards in such a way that switching transient effects are minimized. The recommended methods are gridded power and ground lines or separate power and ground planes. The power and ground lines act like transmission lines to the high frequency transients generated by DRAMs. The impedance is minimized if all the power supply traces to all DRAMs run both horizontally and vertically and are connected at each intersection or better yet if power and ground planes are used.

Address and control lines should be as short as possible to avoid skew. In boards with many DRAMs these lines should fan out from a central point like a fork or comb rather than being connected in a serpentine pattern. Also the control logic should be centrally located on large memory boards to facilitate the shortest possible address and control lines to all the DRAMs.

#### **Decoupling**

The importance of proper decoupling cannot be over emphasized. Excessive transient noise or voltage droop on the  $V_{CC}$  line can cause loss of data integrity (soft errors). The total combined voltage changes over time in the  $V_{CC}$  to  $V_{SS}$  voltage (measured at the device pins) should not exceed 500 mV.

A high frequency  $0.3~\mu\mathrm{F}$  ceramic decoupling capacitor should be connected between the  $V_{CC}$  and ground pins of each 21256 using the shortest possible traces. These capacitors act as a low impedance shunt for the high frequency switching transients generated by the 21256 and they supply much of the current used by the 21256 during cycling.

In addition, a large tantalum capacitor with a value of 47  $\mu$ F to 100  $\mu$ F should be used for bulk decoupling to recharge the 0.3  $\mu$ F capacitors between cycles, thereby reducing power line droop. The bulk decoupling capacitor should be placed near the point where the power traces meet the power grid or power plane. Even better results may be achieved by distributing more than one tantalum capacitor throughout the memory array.

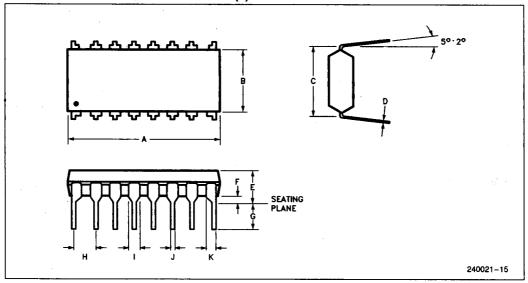

## **PACKAGE DIMENSIONS**

## 16-LEAD PLASTIC DUAL-IN-LINE PACKAGE (P)

| Item | Millimeters  | Inches        |

|------|--------------|---------------|

| Α    | 19.43 ±0.05  | 0.765 ± 0.002 |

| В    | 6.86 ± 0.05  | 0.270 ±0.002  |

| С    | 7.62         | 0.300         |

| D    | 0.25 ± 0.025 | 0.010 ±0.001  |

| E    | 3.56 ± 0.05  | 0.140 ±0.002  |

| F    | 0.506 ±0.1   | 0.020 ±0.004  |

| G    | 3.3 ± 0.1    | 0.130 ±0.004  |

| Н    | 2.54         | 0.100         |

| l    | 1.52         | 0.060         |

| J    | 0.457 ±0.05  | 0.018 ± 0.002 |

| к    | 0.1 ±0.05    | 0.040 ±0.002  |

#### **REVISION SUMMARY**

The following list represents the key differences between version -004 and -005 of the 21256 Data Sheet.

- Deleted 21256-06, 21256-07, and 21256-10 products and specifications.

- 2. Deleted ZIP (Z) and PLCC (N) packages.

- 3. Deleted Sales Office mailing lists.