# 82335 SX HIGH-INTEGRATION INTERFACE DEVICE FOR 386TM SX MICROPROCESSOR BASED PC-AT SYSTEMS

- Operates with the 82230 and 82231 to Provide 100% IBM AT™ Compatibility

- Optimized for 16 MHz and 20 MHz 386™ SX Microprocessor Based PC-AT Systems

- Page Mode, Interleaved DRAM Controller

- Address Mapping/Shadow ROM Support

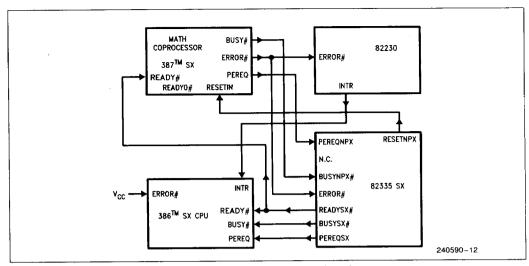

- 387<sup>TM</sup> SX Numeric Coprocessor Synchronization Interface

- Parity Generation and Checking

- Low Power, High Speed CHMOS IV Technology

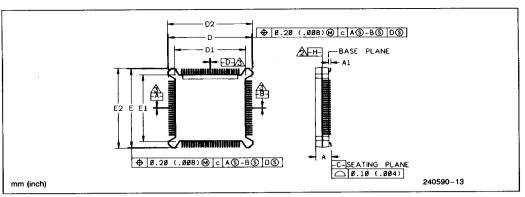

- Available in 132 Lead Plastic Quad Flat Pack

The Intel 82335 SX is a high integration interface device used together with the 82230/82231 to provide the most cost-effective and highest performance system design solution for AT-compatible 386 SX microprocessor based systems. The 82335 SX is plug compatible with the 82335.

The 82335 SX DRAM control feature is designed and optimized for the 16 MHz and 20 MHz 386 SX micro-processor bus architecture. The page mode, interleaved memory design allows 0 wait state performance on most memory accesses with 100 ns DRAM at 16 MHz or 80 ns DRAM at 20 MHz.

Several address mapping options are available to provide flexibility in the system memory size and configuration.

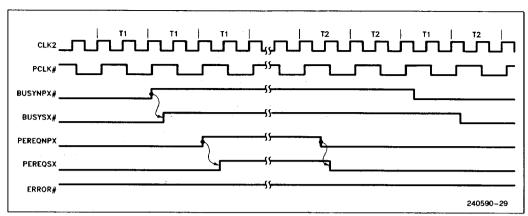

The 82335 SX also provides the necessary interface signals to allow the 387 SX numeric coprocessor to run in a PC/AT system. The 82335 SX with its intergrated parity generation and checking provides system designers with data integrity and reliability.

IBM AT is a trademark of International Business Machines Corporation. 386, 387 are trademarks of Intel Corporation.

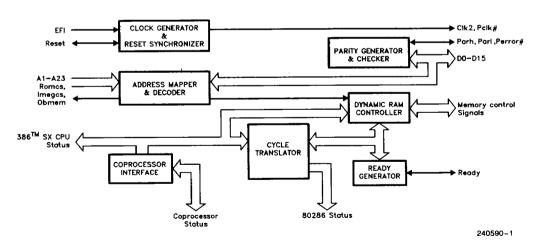

Figure 1.1. 82335 SX Internal Block Diagram

October 1990 Order Number: 240590-002

#### 1.0 PIN DESCRIPTION EXTRDY TURBO# 99 RESETNPX C 0 98 EFI C V<sub>SS</sub> C PCLK# C V<sub>CC</sub> C 2 3 4 5 6 7 5 DO 97 **D** D1 96 D2 D3 D4 D5 95 94 RESETCPU 93 READY286# C 92 8 M/I0286# 91 > D6 V<sub>SS</sub> C S0# V<sub>CC</sub> C ERROR# C 90 **D** D7 10 11 12 89 **→** D8 **D**9 88 87 D10 13 D11 86 14 D12 85 A3 C 15 D13 84 16 17 A4 C D14 83 TOP VIEW A5 C D15 A6 C 18 81 A7 C 19 PĂŘH VSS 80 V<sub>SS</sub> C 20 79 21 78 PARL V<sub>CC</sub> C 22 23 24 25 DEN# 77 76 75 74 73 72 > DIR A10 C CASH3# A11 C CASL3# A12 C A13 C A14 C A15 C 26 RAS3# 27 CASH2# 28 CASL2# 29 RAS2# 70 A16 C 30 69 31 32 33 68 TEST1 A18 C TESTO A19 C RASO# CASLO# CASHO# RAS1# CASL1# CASH1# 240590-2

Figure 1.2. 82335 SX Pin Out Top View

Table 1.1. Alphabetical Pin Assignment

| Address         | Data           | Control      | Control      | V <sub>CC</sub> | V <sub>SS</sub> |

|-----------------|----------------|--------------|--------------|-----------------|-----------------|

|                 | D0 97          | A20GATE 127  | M/IO# 116    | 5               | 3               |

| A1 113<br>A2 14 | D0 97<br>D1 96 | A20GATE 127  | M/IO286# 8   | 12              | 10              |

| A2 14<br>A3 15  | D1 96<br>D2 95 | BHE# 114     | NA# 106      | 22              | 20              |

| A3 15<br>A4 16  | D2 93          | BLE# 112     | OBMEM 40     | 45              | 43              |

| A5 17           | D4 93          | BUSYNPX# 131 | PARH 80      | 51              | 49              |

| A6 18           | D5 92          | BUSYSX# 120  | PARL 78      | 55              | 53              |

| A7 19           | D6 91          | CASH0 60     | PCLK# 4      | 69              | 64              |

| A8 21           | D7 90          | CASH1 63     | PEREQNPX 101 | 81              | 79              |

| A9 23           | D8 89          | CASH2 72     | PEREQSX 121  | 110             | 105             |

| A10 24          | D9 88          | CASH3 75     | PERROR# 124  | 115             | 108             |

| A11 25          | D10 87         | CASLO 59     | RAS0# 58     | 130             | 128             |

| A12 26          | D11 86         | CASL1 62     | RAS1# 61     |                 |                 |

| A13 27          | D12 85         | CASL2 71     | RAS2# 70     |                 |                 |

| A14 28          | D13 84         | CASL3 74     | RAS3# 73     |                 |                 |

| A15 29          | D14 83         | CLK2 109     | READY286# 7  |                 |                 |

| A16 30          | D15 82         | D/C# 117     | N.C. 100     |                 |                 |

| A17 31          |                | DEN# 77      | READYSX# 107 | İ               |                 |

| A18 32          |                | DIR 76       | REFRESH# 123 |                 | 1               |

| A19 33          |                | EFI 2        | RESETCPU 6   |                 |                 |

| A20 34          |                | ERROR# 13    | RESETNPX 1   |                 | •               |

| A21 35          |                | EXTRDY 99    | RESETSX 119  |                 | 1               |

| A22 36          |                | FM 66        | ROMCS0# 39   |                 | İ               |

| A23 37          |                | HLDA 132     | ROMCS1# 38   | ł               |                 |

| MA0 56          |                | HLDASX 103   | S0# 11       |                 |                 |

| MA1 54          | ļ              | HRQ286 122   | S1# 9        |                 |                 |

| MA2 52          |                | HRQSX 104    | SYSRESET 126 |                 |                 |

| MA3 50          |                | LMEGCS# 102  | TESTO 67     |                 |                 |

| MA4 48          |                | MEMR# 125    | TEST1 68     |                 |                 |

| MA5 47          |                | MEMW# 129    | TURBO# 98    |                 |                 |

| MA6 46          |                | MMS 65       | WE# 57       | 1               |                 |

| MA7 44          |                | 1            | W/R# 118     |                 |                 |

| MA8 42          |                |              |              |                 |                 |

| MA9 41          |                |              |              | 1               | <u> </u>        |

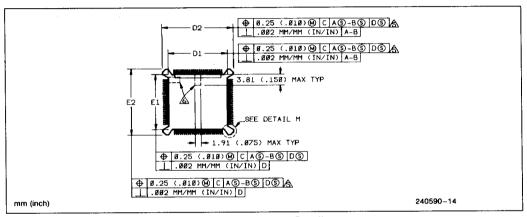

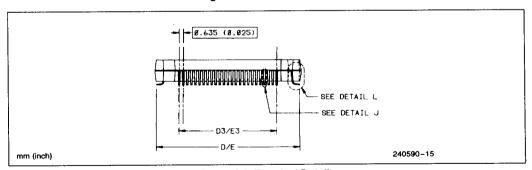

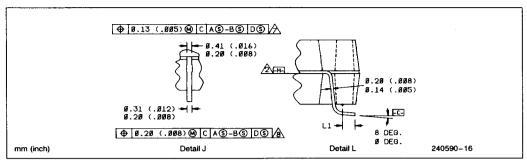

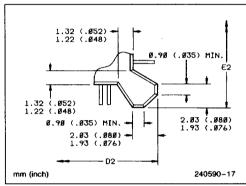

The 82335 SX is implemented in a 132-pin plastic flatpack package designed for direct surface mounting on component boards. The following is a description of the physical pin connections.

Table 1.2. Pin Description

| Symbol  | Pin<br>No.                     | Туре     | Name and Function                                                                                                                                                                                                                                                                    |

|---------|--------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1-A23  | 14-19,<br>21,<br>23-37,<br>113 | <b>*</b> | ADDRESS INPUTS: These inputs are used to select the dynamic RAM address for a memory read or write operation.                                                                                                                                                                        |

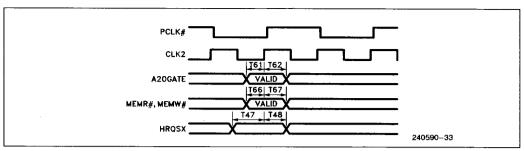

| A20GATE | 127                            | <b>I</b> | ADDRESS 20 GATE: This active high input is used by the keyboard controller to force A20 low. When A20GATE is low, A20 is forced low internal to the 82335 SX during CPU memory cycles (not DMA or master). When A20GATE is high, A20 follows the CPU address input from the A20 pin. |

#### NOTES:

The symbol # following a signal name indicates that the signal is low active.

Table 1.2. Pin Description (Continued)

|                   |                   |      | rable 1.2. Pin Description (Continued)                                                                                                                                                                                                                                                          |

|-------------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin<br>No.        | Туре | Name and Function                                                                                                                                                                                                                                                                               |

| ADS#              | 111               |      | ADDRESS STATUS: This active low input indicates that a valid bus cycle definition and address (W/R#, M/IO#, D/C#, BLE#, BHE#, and A1–A23) is being driven by the 386™ SX microprocessor.                                                                                                        |

| BHE#              | 114               | -    | BYTE HIGH ENABLE: This active low input indicates when data is being transferred on D8-D15.                                                                                                                                                                                                     |

| BLE#              | 112               | I    | BYTE LOW ENABLE: This active low input indicates when data is being transferred on D0-D7.                                                                                                                                                                                                       |

| BUSYNPX#          | 131               | 1    | BUSY NP: This active low input is used by the 387TM SX coprocessor to indicate that it is busy. It is designed to be connected directly to BUSY# of the 387 SX. BUSYNPX# has a weak internal pullup resistor.                                                                                   |

| BUSYSX#           | 120               | 0    | BUSY SX: This active low output indicates to the 386 SX CPU that the 387 SX is busy. It is designed to be connected directly to BUSY # of the 386 SX CPU.                                                                                                                                       |

| CASH0#-<br>CASH3# | 60, 63,<br>72, 75 | 0    | COLUMN ADDRESS STROBE (HIGH BYTE): These outputs are used by the high byte of the dynamic RAM array to latch the column address present on the MA0-MA9 pins. They can drive the dynamic RAM array directly and need no external drivers.                                                        |

| CASL0#-<br>CASL3# | 59, 62,<br>71, 74 | 0    | COLUMN ADDRESS STROBE (LOW BYTE): These outputs are used by the low byte of the dynamic RAM array to latch the column address present on the MA0-MA9 pins. They can drive the dynamic RAM array directly and need no external drivers.                                                          |

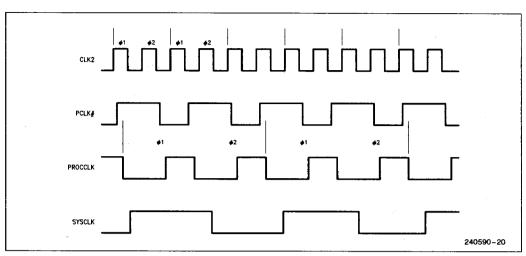

| CLK2              | 109               | 0    | CLOCK2: This output drives the 386 SX and 387 SX input clocks. It is generated by the External Frequency Input (EFI) and outputs the same frequency as EFI (32 MHz or 40 MHz).                                                                                                                  |

| D/C#              | 117               | l    | <b>DATA/CONTROL SELECT:</b> This input from the 386 SX is used to distinguish between data and control bus cycles.                                                                                                                                                                              |

| DEN#              | 77                | 0    | DATA ENABLE: This active low output is used by the data transceivers to enable the transfer of data between the dynamic RAM array and the local data bus.                                                                                                                                       |

| DIR               | 76                | 0    | DIRECTION: This signal is used to control the direction input of the data transceivers which connect the dynamic RAM array to the local data bus. When DIR is high, data is being written into memory.                                                                                          |

| D15-D0            | 82-97             | 1/0  | DATA BUS: These inputs are used by the 82335 SX for parity generation and checking of data which is transferred between the local bus and the DRAM array. During initialization of the 82335 SX, they are used to write/read control words to/from the internal memory configuration registers. |

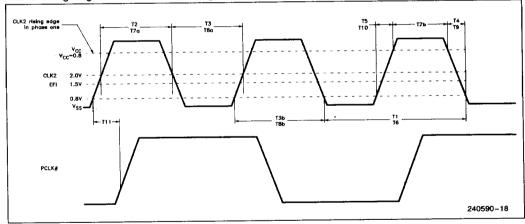

| EFI               | 2                 | 1    | EXTERNAL FREQUENCY IN: This input is driven by an external oscillator. It is used by the 82335 SX to generate the CLK2 and PCLK# output clocks. All internal 82335 SX logic is also driven by EFI. The EFI frequency is the same as the CLK2 (32 MHz or 40 MHz).                                |

| ERROR#            | 13                | 1    | ERROR: This input indicates when a numeric coprocessor error has occurred. ERROR# is designed to be directly connected to the ERROR# output of the 387 SX and ERROR# input of the 82230. ERROR# has a weak pull-up resistor inside the 82335 SX.                                                |

Table 1.2. Pin Description (Continued)

| Symbol    | Pin<br>No.                                    | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|-----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

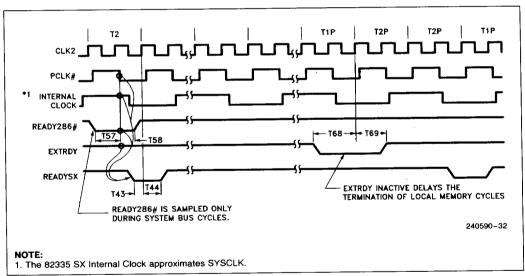

| EXTRDY    | 99                                            | l      | <b>EXTERNAL READY:</b> This is an active high, level triggered input used to insert additional wait states into local memory bus cycles. Deactivation of EXTRDY during a local memory or numerics coprocessor access delays activation of the READYSX# output until EXTRDY is sampled active. Deactivation of EXTRDY will <b>block</b> (not delay) recognition of the READY286# input. |

| FM<br>MMS | 66<br>65                                      | l<br>I | FM and MMS are used to select DRAM operating modes. Refer to the DRAM controller section for available modes. These pins should be static after system reset.                                                                                                                                                                                                                          |

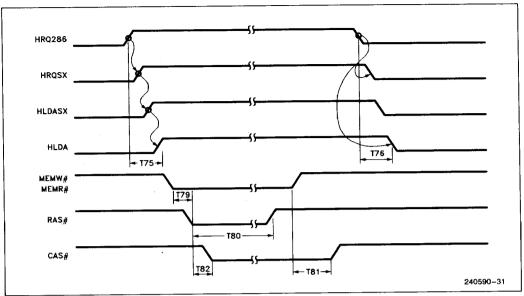

| HLDA      | 132                                           | 0      | HOLD ACKNOWLEDGE: This output indicates the 386 SX has relinquished control of the local bus. It is asserted in response to activation of the HLDASX input from the 386 SX. It is designed to be connected to the 82231 HLDA input.                                                                                                                                                    |

| HLDASX    | 103                                           | I      | HOLD ACKNOWLEDGE SX: This input is asserted by the 386 SX in response to assertion of the 386 SX HOLD pin. It indicates that the processor has relinquished control of the local bus. It is designed to be connected to the 386 SX HLDA output.                                                                                                                                        |

| HRQ286    | 122                                           | i      | CPU HOLD REQUEST INPUT: This active high input receives hold request signals for the 386 SX. It is designed to be driven by CPUHRQ from the 82231.                                                                                                                                                                                                                                     |

| HRQSX     | 104                                           | 0      | CPU HOLD REQUEST OUTPUT: This active high output drives the 386 SX HOLD input. It is the HRQ286 input with the trailing edge delayed.                                                                                                                                                                                                                                                  |

| LMEGCS#   | 102                                           | 0      | LOWER MEG CHIP SELECT: This output is held low during local DRAM accesses made to the first megabyte of memory (000000H-0FFFFH).                                                                                                                                                                                                                                                       |

| MA9-MA0   | 41, 42,<br>44,<br>46–48,<br>50, 52,<br>54, 56 | 0      | MULTIPLEXED ADDRESS: These outputs are designed to provide the row and column addresses for CPU or DMA access, and row addresses for refresh access to the dynamic RAM array.                                                                                                                                                                                                          |

| MEMR#     | 125                                           | t      | MEMORY READ COMMAND: This active low input is used to indicate when a DMA memory read cycle is being performed. It is designed to be connected directly to the —MEMR output of the 82230. MEMR # can be an asynchronous input.                                                                                                                                                         |

| MEMW#     | 129                                           | 1      | MEMORY WRITE COMMAND: This active low input is used to indicate when a DMA memory write cycle is being performed. It is designed to be connected directly to the —MEMW output of the 82230. MEMW # can be an asynchronous input.                                                                                                                                                       |

| M/IO#     | 116                                           | I      | MEMORY/IO SELECT: This input from the 386 SX is used to distinguish between memory and I/O accesses.                                                                                                                                                                                                                                                                                   |

| M/IO286#  | 8                                             | 0      | MEMORY I/O SELECT 286: This output emulates the M/IO# output of the 80286. It is used by the 82230/82231 and other system peripherals to distinguish memory access from I/O access. It is also used with the status output (S0, S1) to indicate halt/shutdown and interrupt acknowledge cycles.                                                                                        |

| NA#       | 106                                           | 0      | NEXT ADDRESS: The NA# output is used to control the address pipelining of the 386 SX. It must be connected to the 386 SX NA# input. Consecutive local memory accesses are always pipelined after the first access.                                                                                                                                                                     |

1

Table 1.2. Pin Description (Continued)

| <del></del>                     |                   | - 1  | able 1.2. Pin Description (Continued)                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                          | Pin<br>No.        | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                        |

| ОВМЕМ                           | 40                | 0    | ON-BOARD MEMORY: This active high output indicates a local DRAM access is in progress.                                                                                                                                                                                                                                                                                   |

| PARH                            | 80                | 1/0  | PARITY HIGH BYTE: This three state input/output is used for the upper byte parity bit of data on the local bus (D8-D15). For memory write cycles, the 82335 SX outputs the internally generated parity bit to the DRAM array via the PARH pin. During a memory read, the 82335 SX uses the data received at PARH to validate the upper byte of data from the DRAM array. |

| PARL                            | 78                | 1/0  | PARITY LOW BYTE: This 3-state input/output is used for the lower byte parity bit of data on the local bus (D0-D7). Its function is identical to the PARH pin described above.                                                                                                                                                                                            |

| PCLK#                           | 4                 | 0    | PERIPHERAL CLOCK: This clock signal is generated by dividing the EFI input by 2 in 16 MHz operation or by 2.5 in 20 MHz operation. It is designed to drive the X3 input of the 82230.                                                                                                                                                                                    |

| PEREQNPX                        | 101               | l    | PROCESSOR EXTENSION REQUEST NP: This input is used by the 387 SX to indicate that it requires a data transfer. It is designed to be connected directly to PEREQ of the 387 SX.                                                                                                                                                                                           |

| PEREQSX                         | 121               | 0    | PROCESSOR EXTENSION REQUEST SX: This output to the 386 SX processor is used to request a data transfer to or from the numeric coprocessor. It is designed to be connected directly to PEREQ of the 386 SX.                                                                                                                                                               |

| PERROR#                         | 124               | 0    | PARITY ERROR: This active low output indicates that the 82335 SX has detected a parity error in either the upper or lower byte of data from the DRAM array. It is designed to drive the 82231 DPCK # input.                                                                                                                                                              |

| RAS0#-<br>RAS3#                 | 58, 61,<br>70, 73 | 0    | ROW ADDRESS STROBE: These outputs are used by the dynamic RAM array to latch the row address present on the MA0-MA9 pins. The four outputs support up to a four-way interleaved dynamic RAM configuration with page-mode access. They drive the dynamic RAM array directly and need no external drivers.                                                                 |

| READY286#                       | 7                 | ı    | <b>READY 286:</b> This active low input is used to indicate the completion of system I/O or memory bus cycles. It is designed to be driven by the 82230 READY # pin.                                                                                                                                                                                                     |

| N.C.<br>(formerly<br>READYNPX#) | 100               | ļ    | NO CONNECT: This pin is not internally connected. The 82335 SX will generate READYSX # after 1 wait-state on all numerics coprocessor accesses if a coprocessor is present in the system.                                                                                                                                                                                |

| READYSX#                        | 107               | 0    | READY SX: This active low output indicates the completion of the current bus cycle to the processor. It is a function of the internally generated ready signal for local memory, on-chip I/O, or coprocessor accesses, and the READY286#, EXTRDY, and TURBO# inputs.                                                                                                     |

| REFRESH#                        | 123               | 1    | REFRESH: This active low input is used to notify the dynamic RAM controller that the dynamic RAM array requires refresh. It is designed to be driven by the 82231 — REFRESH output.                                                                                                                                                                                      |

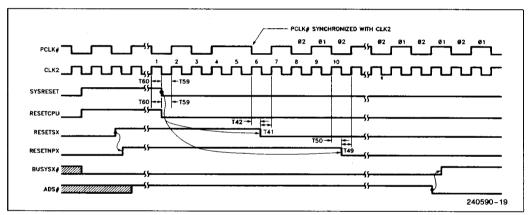

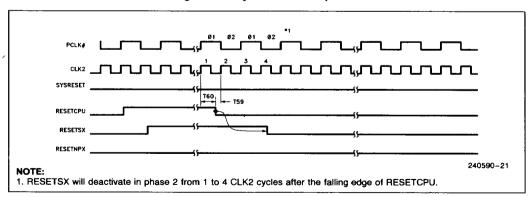

| RESETCPU                        | 6                 | ı    | RESET CPU: This high active input is used to generate the RESETSX output which resets the 386 SX CPU. It must be activated with SYSRESET during power-on reset. After power-on, activation of RESETCPU without SYSRESET will activate RESETSX without RESETNPX. RESETCPU is designed to be driven by the 82230 RES CPU output.                                           |

Table 1.2. Pin Description (Continued)

| Symbol             | Pin                                                         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                  |

|--------------------|-------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | No.                                                         |      | DECETIAL in of the                                                                                                                                                                                                                                                                                                                 |

| RESETNPX           | 1                                                           | 0    | RESET NPX: This output is designed to drive the RESETIN pin of the 387 SX. It is activated only when SYSRESET and RESETCPU are both active.                                                                                                                                                                                        |

| RESETSX            | 119                                                         | 0    | <b>RESET SX:</b> This output is designed to drive the RESET pin of the 386 SX processor. It is a function of the SYSRESET and RESETCPU inputs.                                                                                                                                                                                     |

| ROMCS0#<br>ROMCS1# | 39<br>38                                                    | 0    | ROM CHIP SELECT: These outputs are used to support shadow RAM. They select the ROMs or EPROMs during system initialization. If ROM shadowing is selected, the ROMCS0-1 outputs are disabled and the ROM (EPROM) addresses are mapped into the DRAM physical address space by the 82335 SX.                                         |

| S0#<br>S1#         | 11<br>9                                                     | 0    | BUS CYCLE STATUS: The S0 # and S1 # outputs indicate the initiation of a system (non-local) bus cycle and, along with M/IO286 #, define the type of bus cycle.                                                                                                                                                                     |

| SYSRESET           | 126                                                         |      | SYSTEM RESET: This high active input is combined with RESETCPU to generate the RESETSX and RESETNPX outputs as well as synchronize the clock outputs. SYSRESET is designed to be driven by the 82230 + RESET output.                                                                                                               |

| TEST0<br>TEST1     | 67<br>68                                                    |      | <b>TEST MODE:</b> These inputs are used for special test modes, and must be connected to V <sub>SS</sub> during normal operation. TEST0 is a high active, level triggered input that disables all 82335 SX output buffers when active. The TEST1 input is reserved and must be connected to V <sub>SS</sub> .                      |

| TURBO#             | 98                                                          | 1    | TURBO MODE SELECT: This active low input, when asserted, allows the 386 SX local bus to run with maximum performance. Deactivating the TURBO # input causes the 82335 SX READY generation logic to insert additional wait states into each bus cycle. In the non-turbo mode, 386 SX performance approximates 80286 bus efficiency. |

| Vcc                | 5, 12,<br>22, 45,<br>51, 55,<br>69, 81,<br>110, 115,<br>130 |      | POWER SUPPLY: 11 V <sub>CC</sub> pins total.                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>    | 3, 10,<br>20, 43,<br>49, 53,<br>64, 79,<br>105, 108,<br>128 | _    | GROUND: 11 V <sub>SS</sub> pins total.                                                                                                                                                                                                                                                                                             |

| WE#                | 57                                                          | 0    | WRITE ENABLE: This output is used by the dynamic RAM array to enable input for a write operation. It is designed to drive two banks of DRAM with no additional buffering.                                                                                                                                                          |

| W/R#               | 118                                                         | ı    | <b>WRITE/READ SELECT:</b> This input from the 386 SX is used to distinguish between read and write cycles.                                                                                                                                                                                                                         |

#### 2.0 FUNCTIONAL DESCRIPTION

#### 2.1 Introduction

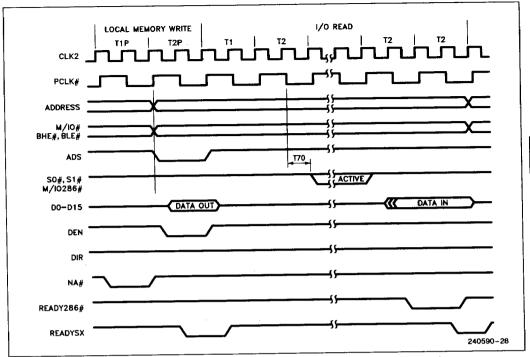

The 82335 SX is a high-integration VLSI companion chip for the Intel 386 SX 32-bit microprocessor. It interfaces the 386 SX microprocessor to the 387 SX numeric coprocessor and to the 82230/82231 highly integrated peripherals to form an AT compatible system. The 82335 SX accomplishes this by converting 386 SX processor bus cycles to 80286 compatible cycles, generating necessary clock signals, and providing local dynamic memory control. Figure 2.1 shows a block diagram of this system.

The 82335 SX is composed of seven functional blocks:

- 1. DRAM Controller

- 2. Address Mapper/Decoder

- 3. Ready Generator

- 4. Bus Cycle Translator

- 5. Math Coprocessor Interface

- 6. Clock Generator/Reset Synchronizer

- 7. Parity Generator/Checker

Each functional block is described in the following sections.

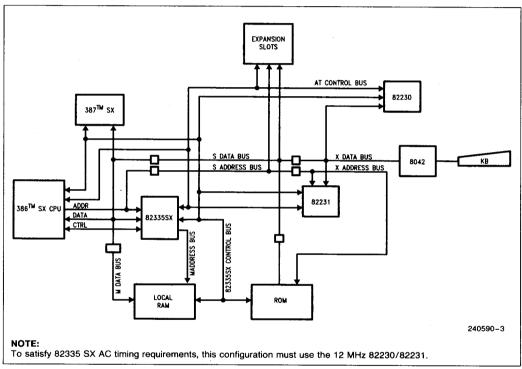

Figure 2.1. 386™ SX CPU with 82335 SX System Block Diagram

#### 2.2 DRAM Controller

#### 2.2.1 INTRODUCTION

The 82335 SX dynamic RAM (DRAM) controller is designed and optimized for the Intel 386 SX Architecture. It keeps track of 386 SX CPU bus states and provides the necessary signals to address and refresh up to four 16-bit banks of 256K or 1M dynamic RAMs.

To optimize memory performance and flexibility, the DRAM controller has built in support for both paging and bank interleaving, and can be configured for several different modes of operation. These include four different memory modes to accommodate DRAM with different levels of performance: F1 and F4 are for either 100 ns (16 MHz) or 80 ns (20 MHz) fast page-mode DRAMs. WO1 and WO2 are for slower DRAMs. These modes are described in more detail in the DRAM mode configuration section.

In addition to the four memory modes available, the DRAM controller can be configured to operate in either turbo or non-turbo mode. The turbo mode allows the 386 SX microprocessor based system to run at peak efficiency, while the non-turbo mode allows it to approximate 80286 bus cycle timing for timing dependent software.

#### 2.2.2 DRAM BANK CONFIGURATION

The local Dynamic RAM for the 386 SX/82335 SX system can be configured into one, two, or four 16-bit banks. Each 16-bit bank of memory is further divided into two 8-bit banks, low and high. Each 8-bit bank may contain one extra bit for parity.

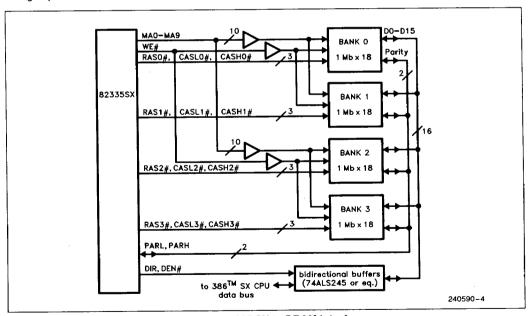

Either 1 Mbyte or 256 Kbyte DRAM may be used. The same type of DRAM must be used in all banks installed. See Figure 2.2 for a block diagram of the 82335 SX to DRAM interface.

The exact memory configuration (DRAM size and number of banks installed) can be determined during system initialization through execution of a memory autoscan routine in the BIOS. Memory configuration information can then be programmed into the memory configuration register, roll compare registers, and address compare registers. See the address mapping/decoding section for details on register programming.

For local memory accesses the 82335 SX generates the DRAM control signals Row address strobe (RAS#), Column address strobe low and high (CASL# and CASH#), and Write enable (WE#), as well as the multiplexed row and column addresses (MA). Each bank has its own separate RAS#,

Figure 2.2. 82335 SX to DRAM Interface

Table 2.1. Address to Multiplexed Address Translation

| Size   Banks                                               |        |     |     | ď   | ow Ac | Row Address |     |     |            | -   |           |            |            | ဒ္ဓ        | Column Address | ddre       | SS         |            |            |        | Bank       | ¥ to |

|------------------------------------------------------------|--------|-----|-----|-----|-------|-------------|-----|-----|------------|-----|-----------|------------|------------|------------|----------------|------------|------------|------------|------------|--------|------------|------|

| F1/F4 256K 1<br>F1/F4 256K 2<br>F1/F4 256K 4<br>F1/F4 1M 1 | (S MA9 | MA8 | MA7 | MA6 | MA5   | MA4         | MA3 | MA2 | MA1        | MAO | MA9       | MA8        | MA7        | MA6        | MA5 N          | MA4        | MA3        | MA2        | MA1        | MAO    | <b>8</b>   | 8    |

| F1/F4 256K 2<br>F1/F4 256K 4<br>F1/F4 1M 1                 |        | A10 | A11 | A12 | A18   | A17         | A16 | A15 | A14        | A13 |           | 9A         | 48         | A7         | A6             | A5         | <b>A4</b>  | A3         | A2         | A1     |            | 0    |

| F1/F4 256K 4 F1/F4 1M 1                                    |        | A19 | A11 | A12 | A18   | A17         | A16 | A15 | A14        | A13 |           | A9         | <b>A8</b>  | <b>A</b> 7 | 9e             | A5         | <b>4</b> 4 | A3         | <b>4</b> 2 | ٦<br>۲ |            | A10  |

| F1/F4 1M 1                                                 |        | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 |           | Α9         | <b>A8</b>  | <b>A</b> 7 | ye             | A5         | <b>4</b> 4 | <b>A</b> 3 | <b>4</b> 2 | F      | A11        | A10  |

| C 111                                                      | A11    | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 | A10       | <b>4</b> 9 | <b>A8</b>  | <b>A</b> 7 | <b>A6</b>      | A5         | <b>4</b> 4 | <b>A</b> 3 | <b>A</b> 2 |        |            | 0    |

| 7 MI 51/11                                                 | A21    | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 | A10       | <b>A</b> 9 | <b>A8</b>  | Α7         | ye<br>Ye       | A5         | <b>4</b> 4 | A3         | <b>4</b> 2 | ¥      | 0          | F    |

| F1/F4 1M 4                                                 | A21    | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 | A10       | Α9         | Α8         | <b>A</b> 7 | ye<br>Ye       | <b>A</b> 5 | <b>A</b> 4 | A3         | <b>A</b> 2 |        |            | A11  |

| WO1/WO2 256K 1                                             |        | A10 | A11 | A12 | A18   | A17         | A16 | A15 | A14        | A13 |           | A9         | <b>A8</b>  | Α7         | A6             | A5         | <b>A</b> 4 | A3         | <b>4</b> 2 |        |            | 0    |

| WO1/WO2 256K 2                                             |        | A19 | Ä   | A12 | A18   | A17         | A16 | A15 | A14        | A13 |           | Α9         | <b>48</b>  | <b>A</b> 7 | A6             | A5         | <b>A</b> 4 | Аз         | <b>4</b> 2 |        |            | ¥    |

| WO1/WO2 256K 4                                             | -      | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 |           | A9         | <b>48</b>  | Α7         | ye<br>Ye       | A5         | <b>44</b>  | Ą3         | 41         |        |            | ₹    |

| WO1/WO2 1M 1                                               | A11    | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 | A10       | <b>4</b> 9 | <b>A</b> 8 | <b>4</b> 2 | <b>A6</b>      | A5         | <b>4</b> 4 | A3         | <b>4</b> 5 |        |            | 0    |

| WO1/WO2 1M 2                                               | A21    | A19 | A20 | A12 | A18   | A17         | A16 | A15 | A14        | A13 | <b>41</b> | <b>A</b> 9 | <b>A8</b>  | <b>A</b> 7 | <b>A6</b>      | A5         | <b>A</b> 4 | A3         | <b>4</b> 5 | A10    |            | ¥    |

| WO1/WO2 1M 4                                               | A21    | A19 | A20 | A22 | A18   | A17         | A16 | A15 | <b>A14</b> | A13 | A10       | <b>8</b>   | <b>A8</b>  | <b>A</b> 7 | 9e             | A5         | <b>A4</b>  | A3         | <b>A11</b> | A10    | <b>A</b> 2 | A1   |

1-90

CASL#, and CASH# signals. The RAS#, CASL#, and CASH# outputs can directly drive the DRAM.

The WE# and Multiplexed Address lines are common to all banks. These outputs can directly drive approximately two banks of memory. If the capacitive loading on these outputs exceeds the maximum loadings defined in the AC timing specifications, then they will need to be buffered.

The multiplexed address outputs (MA0-MA9) are derived from the address inputs A1-A23 during local memory read or write operations. The way the 82335 SX translates the address inputs into row address, column address, and bank select bits depends upon several factors. These factors include DRAM size, number of banks installed, and mode of operation. Table 2.1 shows how the input addresses are translated.

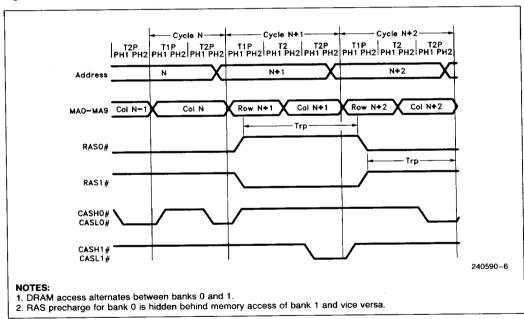

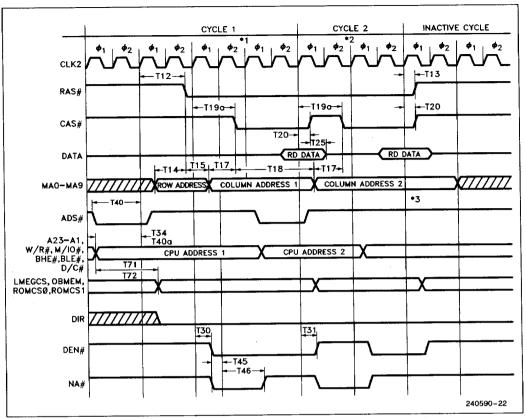

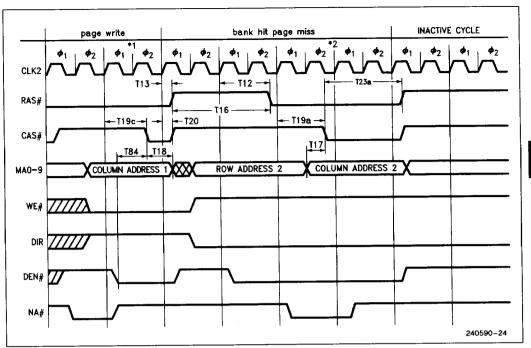

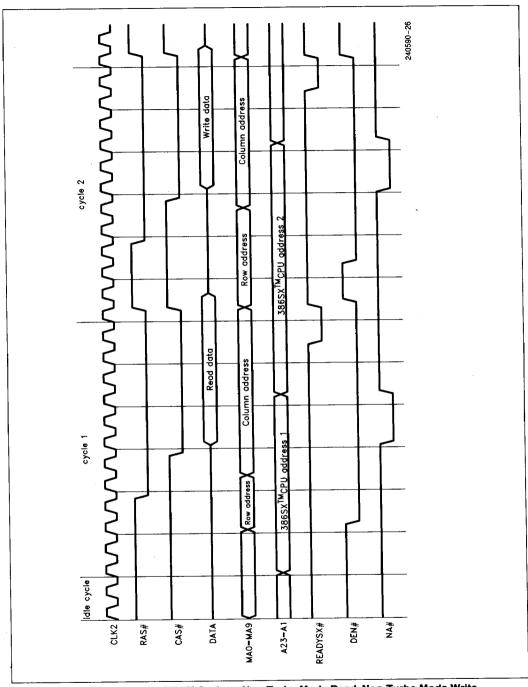

#### 2.2.3 PAGE-MODE DRAM OPERATION

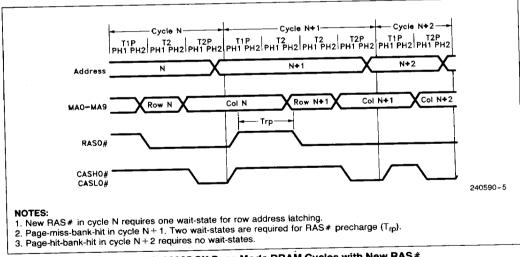

Every DRAM access requires that the DRAM be provided with both a row address and a column address. A DRAM access requiring both a new row address and new column address has a long cycle time which requires at least one wait state. Figure 2.3 shows examples of DRAM cycles that require both new row and new column addresses.

The 82335 SX significantly improves bus performance by "paging" row addresses. Memory locations sharing the same row address are in the same "memory page". When successive memory accesses are in the same page (a page-hit memory access), only a new column address is required. This way, the row address strobe, RAS#, can be kept active, and each page-hit memory cycle only requires a new column address. This reduces the memory access time and allows most memory cycles to run at zero wait states. Figure 2.3 shows examples of both page-hit and page-miss cycles.

The effectiveness of page-mode operation in reducing wait states is dependent upon several factors. The most important factors are page location, page size, and page-mode cycle time. Page location and size are discussed below and page-mode cycle time is discussed in Section 2.2.4.

Page location is determined by the selection of address bits used for DRAM row addresses. To increase page-hits (zero wait state cycles), pages should be located such that successive memory accesses are in the same page. The 82335 SX generates row addresses from the higher order address bits. Since these bits are less likely to change than the lower order address bits, this increases the page-hit rate.

The page-hit rate can also be increased by increasing the page size. The page size for a single bank is 1 KByte if 256K DRAM chips are installed and 2 KByte if 1M DRAM chips are installed. The 82335 SX can keep a page of memory active in each bank. This can double the effective page size in a two bank configuration. A four bank configuration can effectively increase the page size by a factor of four. This increase in the active page size can significantly improve system performance. A memory access to an active page in a different bank (a page-hit-bank-miss) only requires a new column address, and therefore runs at zero wait states.

The 82335 SX keeps a memory page active for a particular bank by holding the RAS# signal active for that bank. The RAS# signal for a bank is activated by either an access to that particular bank or by a memory refresh.

RAS# deactivation can be caused by a number of events. In non-turbo mode RAS# is always deactivated at the end of each memory cycle. In turbo mode RAS# is deactivated by a page-miss memory cycle, RAS# timeout, or ending successive local memory accesses.

In addition to the RAS# deactivation events in turbo mode, F1 mode will also deactivate the RAS# signal for the previously accessed bank when a bank switch occurs.

A page-miss memory cycle in modes F4, WO1, and WO2 will deactivate the RAS# signal only for the bank currently being accessed. Wait states are then inserted into the memory cycle to insure that the minimum RAS# precharge time required by the DRAM is satisfied.

RAS# deactivation can also be caused by a "RAS# timeout". Dynamic RAM chips have a limit on the maximum time that RAS# can be held active. The 82335 SX controls RAS# active time with four built-in watch-dog timers. Once timed-out, a RAS# signal will deactivate at the end of the current memory cycle. Each timer operates independently and guarantees a maximum RAS# active time of 10 µs.

RAS# signals that have been activated in mode F4, WO1, or WO2 and have not been timed-out, will remain active while successive local memory accesses are made. If the CPU executes a bus cycle other than a local memory cycle (i.e., I/O cycle, system memory cycle, etc.) or the CPU bus enters a hold or idle state, then all RAS# signals will deactivate. Table 2.2 summarizes RAS# activation.

Table 2.2. RAS# Activation

| Mode                    | When                                                    | What                                     |

|-------------------------|---------------------------------------------------------|------------------------------------------|

|                         | _                                                       |                                          |

| RAS# Activation         |                                                         | RAS# for that bank is activated.         |

| All Modes               | <ul> <li>A memory access is made to a bank.</li> </ul>  |                                          |

|                         | <ul> <li>A memory refresh is initiated.</li> </ul>      | All RAS# signals are activated.          |

| RAS# De-Activa          | ation                                                   |                                          |

| Non-Turbo               | <ul> <li>End of each local memory<br/>cycle.</li> </ul> | All RAS# are de-activated.               |

| Turbo F4,<br>Turbo WO1, | A page-miss occurs.                                     | RAS# is de-activated for that bank.      |

| Turbo WO2               | A RAS# timeout occurs.                                  | RAS# is de-activated for that bank.      |

|                         | Any cycle other than a local                            | All RAS# signals are de-<br>activated.   |

|                         | memory access.                                          |                                          |

| Turbo F1                | A bank switch occurs.                                   | RAS# de-activates for the previous bank. |

|                         | A page-miss occurs.                                     | RAS# is de-activated for that bank.      |

|                         | A RAS# timeout occurs.                                  | RAS# is de-activated for that bank.      |

|                         | Any cycle other than a local                            | All RAS # signals are de-<br>activated.  |

Figure 2.3. 82335 SX Page Mode DRAM Cycles with New RAS#, Page Miss, and Page Hit Cycles in F1/F4 Modes

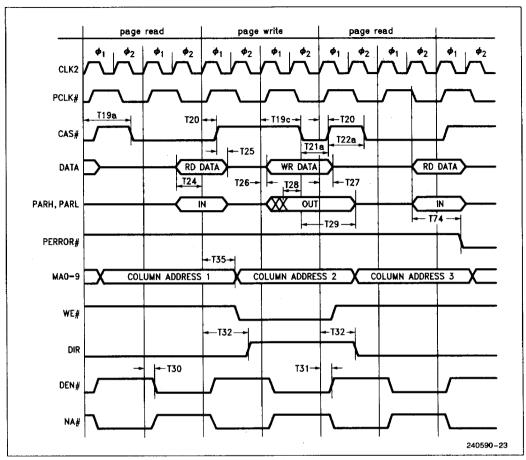

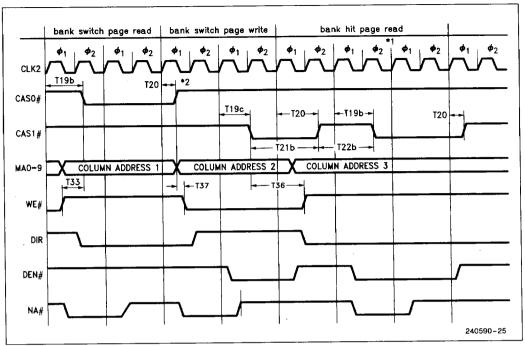

## 2.2.4 PAGE-MODE BANK INTERLEAVE OPERATION

Most fast page-mode DRAM have short cycle times which allow zero wait-state bus cycles on successive DRAM accesses. Slower DRAM, however, have longer cycle times which require wait-states to be inserted between successive accesses to the same memory bank. The 82335 SX allows most memory accesses to occur at zero wait-states, even for slow DRAM, by "interleaving" memory banks.

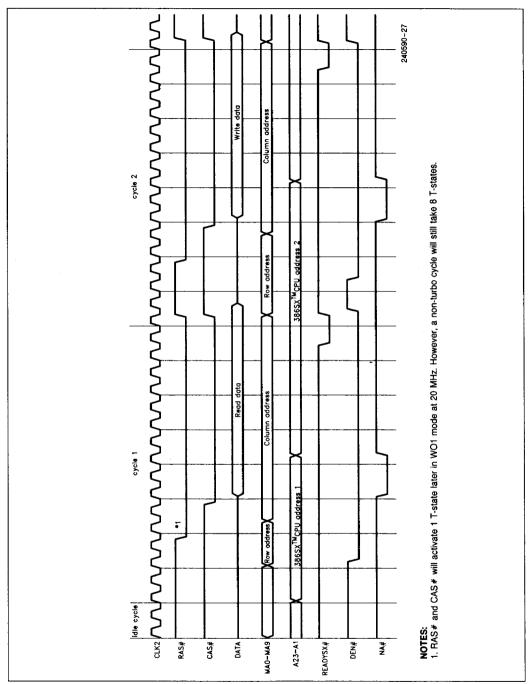

Interleaving refers to alternating bank accesses. Multi-bank configurations are always interleaved. In fast mode (F4/F1), banks are interleaved in pages. In slow mode (WO1/WO2), the lower address bit(s) are used to interleave banks by words (two bytes). Word interleaving alternates bank-hits for consecutive memory accesses thereby increasing the cycle time available to slow DRAM. This increases the number of zero wait-state page-hit-bank-miss cycles and improves system performance. Table 2.1 shows the address bits used for bank selection. An example of two bank interleaving in F1 mode is shown in Figure 2.4.

#### 2.2.5 DRAM MODE CONFIGURATION

The 82335 SX can be configured to run in four different modes to operate with DRAM of various performance levels. This allows the system designer considerable flexibility. There are two modes (F1 and F4) for fast page mode DRAM and two modes (W01 and W02) for slower DRAM. The mode of operation is selectable by setting the input pins FM and MMS to the values shown in Table 2.3. Tables 2.3A and 2.3B show a summary of the different DRAM modes. A brief description of each mode follows.

F4: This is a high performance mode for fast 100 ns DRAM at 16 MHz or fast 80 ns DRAM at 20 MHz. The critical timing specifications that determine which DRAM can use this mode are listed in Tables 2.3A and 2.3B. Mode F4 allows up to four memory pages to be active simultaneously. This increases the page hit rate and allows more memory cycles to run at zero wait-states.

F1: This mode works with the same fast DRAM as mode F4. It differs from mode F4 in that only

Figure 2.4. 82335 SX DRAM Cycle with Interleaved Memory in F1 Mode

one memory page can be kept active at a time. Activating only one page at a time reduces power consumption. Since only one page is kept active at a time, any bank-miss is also a page-miss which requires at least one wait-state.

WO1: Mode WO1 can be used with all 100 ns DRAM at 16 MHz or all 80 ns DRAM at 20 MHz. Slow page-mode DRAM that don't meet the critical specifications required for modes F4 and F1 can be used in mode WO1. This mode inserts one wait-state in page-hit-bank-hit cycles to allow the DRAM sufficient cycle time. At 20 MHz this mode also inserts one wait-state in page miss cycles to correspond to DRAM specifications. Up to four memory pages can be kept active simultaneously in this mode.

WO2: This mode allows inexpensive 120 ns DRAM to be used with the 82335 SX. It inserts additional wait-states in all cycles except page-hit-bank-miss cycles which run at zero wait-states. At 20 MHz there is no WO2 mode. At 20 MHz, if FM = 0, the 82335 SX will operate in WO1 mode regardless of the state of MMS. Up to four memory pages can be kept active simultaneously in this mode.

#### 2.2.6 NON-TURBO MODE

Some programs written for 80286 based machines have software timing loops that are sensitive to processor speed. The 82335 SX non-turbo mode feature allows it to slow down local memory accesses to approximate 80286 bus timing.

The 82335 SX is put into non-turbo mode by driving the TURBO# input high (TURBO# >  $V_{IH}$ ). The TURBO# input is then latched internally to synchronize it with DRAM accesses. It is latched on the falling edge of the 82335 SX HLDA output. This allows TURBO# to be an asynchronous input. Once the TURBO# input has been sampled high, a fixed number of bus states (six per memory cycle at 16 MHz or eight per memory cycle at 20 MHz) will be used for local memory accesses. The TURBO# input does not affect DMA cycle time. Figures 4.7A and 4.7B in the A.C. timing diagram section show examples of non-turbo mode read and write cycles.

#### 2.2.7 REFRESH CYCLE

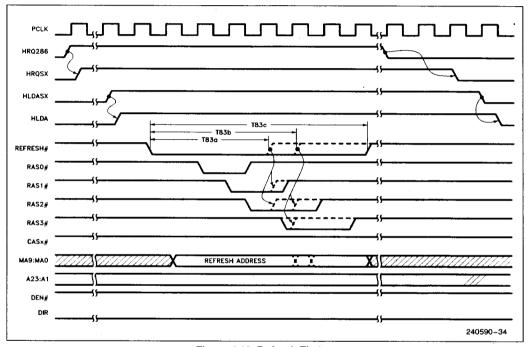

The 82335 SX controls DRAM refreshing in addition to controlling DRAM accesses. A DRAM refresh is initiated by asserting a hold request (HRQ266), receiving a hold acknowledge (HLDA), and then pulsing the REFRESH# input low. The 82335 SX then performs a "RAS only" refresh (no CAS# signals are generated). Once the refresh is completed (all banks have received a RAS# pulse), the REFRESH# and HRQ286 inputs can be deasserted. REFRESH# should not be asserted until the hold request has been acknowledged by the 82335 SX. Once asserted, the REFRESH# input must be held active for the minimum refresh period (see specification T83 in the A.C. specification section).

Table 2.3A. 16 MHz Summary of DRAM Modes

|    |     |      | Max    |          | Wa        | it States |           |     |                          | Critical                                                                                                             |

|----|-----|------|--------|----------|-----------|-----------|-----------|-----|--------------------------|----------------------------------------------------------------------------------------------------------------------|

| FM | MMS | Mode |        | Pag      | ge Hit    | Page      | e Miss    | New | DRAM Type                | DRAM                                                                                                                 |

|    | '   |      | Active | Bank Hit | Bank Miss | Bank Hit  | Bank Miss | RAS |                          | Specifications                                                                                                       |

| 1  | 1   | F4   | 4      | 0        | 0         | 2         | 2         | 1   | 100 ns Fast<br>Page Mode | $t_{CAS} \le 35 \text{ ns}$<br>$t_{CAC} \le 35 \text{ ns}$<br>$t_{CP} \le 20 \text{ ns}$                             |

| 1  | 0   | F1   | 1      | 0        | NA ·      | 2         | 1         | 1   | 100 ns Fast<br>Page Mode | $\begin{array}{c} t_{CAS} \leq 35 \text{ ns} \\ t_{CAC} \leq 35 \text{ ns} \\ t_{CP} \leq 20 \text{ ns} \end{array}$ |

| 0  | 1   | W01  | 4      | 1        | 0         | 2         | 2         | 1   | All 100 ns DRAM          |                                                                                                                      |

| 0  | 0   | W02  | 4      | 2        | 0         | 3         | 3         | 2   | 120 ns DRAM              |                                                                                                                      |

Table 2.3B. 20 MHz Summary of DRAM Modes

|    |     |      | Max    |          | Wa        | it States |           |     |                                           | Critical                                                                                                                                                                                                            |

|----|-----|------|--------|----------|-----------|-----------|-----------|-----|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FM | ммѕ | Mode |        | Pag      | ge Hit    | Pag       | e Miss    | New | DRAM Type                                 | DRAM                                                                                                                                                                                                                |

|    |     |      | Active | Bank Hit | Bank Miss | Bank Hit  | Bank Miss | RAS |                                           | Specifications                                                                                                                                                                                                      |

| 1  | 0   | F4   | 1      | 0        | 0<br>NA   | 2         | 1         | 1   | 80 ns Fast<br>Page Mode                   | $\begin{aligned} t_{CAC} &\leq 30 \text{ ns} \\ t_{CP} &\leq 20 \text{ ns} \\ t_{CAS} &\leq 30 \text{ ns} \\ t_{RP} &\leq 45 \text{ ns} \\ t_{AA} &\leq 75 \text{ ns} \\ t_{RSH} &\leq 30 \text{ ns} \end{aligned}$ |

| 0  | X   | W01  | 4      | 1        | 0         | 3         | 3         | 2   | All 80 ns DRAM<br>and some<br>100 ns DRAM |                                                                                                                                                                                                                     |

- 1. This table assumes the following input status: TURBO# ≤ V<sub>IL</sub> max., EXTRDY ≥ V<sub>IH</sub> min.

2. The first local memory access following an idle cycle or bus cycle other than a local memory access requires one extra wait-state to switch from non-pipelined to pipelined operation.

- 3. Definitions:

- New RAS = The RAS# signal for a given bank transitions from an inactive to an active state.

- Page hit = An access made to an active memory page.

- Page miss = An access made to a memory page that is not currently active.

- Bank hit = An access to the same memory bank accessed in the immediately preceding bus cycle.

- Bank miss = An access to a memory bank that was not immediately preceded by an access to the same bank.

- = Column Address Strobe pulse width. TCAS

- = Column Address Strobe access time. TCAC

- = Column Address Strobe precharge time. TCP

- = Row Address Strobe precharge time. TRP

- = Column Address access time.  $T_{AA}$

- = Row Address Strobe hold time. TRSH

The 82335 SX generates its own refresh addresses. A ten bit refresh address counter within the 82335 SX is incremented by one at the beginning of every refresh. The refresh address appears on the address lines MA0-MA9 (MA0-MA8 if 256K DRAM are used) and is followed by RAS# activation. The address inputs A23:A1 are ignored during refresh.

During a refresh cycle, each bank of memory is refreshed when its RAS# signal activates. The 82335 SX staggers RAS# activation to reduce current surge during refresh. RAS# activation for each memory bank is separated by one PCLK# clock cycle and remains active for approximately two PCLK# cycles. All RAS# signals are activated during a refresh cycle if the REFRESH# input is held active long enough (see A.C. timing specification T83). If less than four memory banks are installed, the REFRESH# input may be de-activated after the installed banks have been refreshed. When the RE-FRESH# input is de-activated, any active RAS# signals will de-activate and the refresh cycle will be truncated. Figure 4.13 in the A.C. timing diagram section shows refresh timing.

#### 2.3 Address Mapper/Decoder

#### 2.3.1 INTRODUCTION

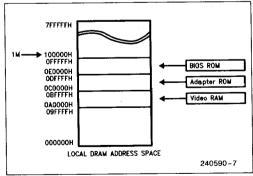

Several address mapping and decoding options are provided to improve performance and allow flexibility in the system memory size and configuration. These options include ROM/EPROM shadowing, mapping up to 512K addresses above the top of physical memory into physical addresses, and decoding input addresses to generate chip select signals. Selection of these options is done via programming of the configuration, roll compare, and address compare registers.

#### 2.3.2 SHADOWING

Shadowing refers to copying data from slow memory devices like ROM and EPROM memories into RAM to speed up memory accesses. Since access to local RAM is much faster than ROM, this can improve BIOS performance considerably. The 82335 SX has built-in support for shadowing three different areas of memory: BIOS ROM, adapter ROM, and video RAM. Figure 2.5 shows the memory address ranges for each area. At least one megabyte of local memory must be installed to use the shadowing feature.

Shadowing can be done in two ways, each with different granularity. For 128 Kbyte granularity, shadowing can be selected for the BIOS ROM area (0E0000H-0FFFFFH), adapter ROM area (0C0000H-0DFFFFH), or video RAM area

(0A0000H-0BFFFFH) by programming the configuration register bits ROMEN\*, ENADP\*, and ENV\* respectively. If the configuration register bit for an area is cleared, then any access to an address in that area will be from ROM (or from system video RAM for the video area). If the configuration register bit for an area is set, then any access to that area will be from local memory. Each area can be shadowed independently. Note this matches 82335 shadowing exactly.

The second way has granularity of 32 Kbyte. The granularity is selected by programming the EXGRAN bit (bit 0) of the Granularity Enable register (I/O address 2CH). If EXGRAN = 0, then 128 Kbyte shadowing as discussed in the previous paragraph is used. The 82335 SX powers up with EXGRAN = 0. If EXGRAN = 1 then 32 Kbyte granularity is used.

If 32 Kbyte granularity is used, video RAM is shadowed the same way as in the 128 Kbyte granularity configuration. Shadowing of the BIOS and adaptor ROM areas is implemented in 32 Kbyte granularity by programming the Extended Granularity register (I/O address 2EH). Each bit in the register controls shadowing of one 32 Kbyte segment in the address range 0C0000H-0FFFFH. The ENADP# and ROMEN# bits in the configuration register must be high if any 32 Kbyte segment in the respective address range needs to be shadowed. Section 2.3.4.4 and 2.3.4.5 contain more information on the Granularity Enable Register and the Extended Granularity Register respectively.

The BIOS ROM area FE0000H-FFFFFFH is addressable regardless of the shadow options selected. An access to an address in this region will always be from ROM.

When shadowing the BIOS ROM and adapter ROM, the ROM contents must be copied to the shadow RAM area. Since an access to one of these areas will access either the ROM or the RAM (not both), the following steps can be used to copy the ROM contents to the shadow area.

#### COPY BIOS ROM

- a. Set configuration register to reflect correct DRAM size and number of banks installed, and clear the ROMEN# bit (enable BIOS ROM access).

- Set address range compare registers to top of local memory (at least 1 MByte).

- c. Copy contents of BIOS ROM to a temporary buffer in low memory (e.g., 040000h-05FFFFh).

- d. Jump to code in temporary buffer to continue execution while enabling shadowing.

- e. Set the ROMEN# bit in the configuration register to enable BIOS shadowing.

- f. If 32 Kbyte granularity is desired

- 1. Set EXGRAN = 1.

- Set the shadow bits in the Extended Granularity register that correspond to the address range desired for shadowing.

- g. Copy contents of temporary buffer to BIOS shadow RAM area.

- h. Jump back to high memory to execute code from BIOS shadow RAM area.

- i. If 32 Kbyte granularity was selected, set the writeprotect bits in the Extended Granularity register that correspond to the address range desired for write-protecting.

#### **COPY ADAPTER ROM**

- a. Set configuration register to reflect correct DRAM size and number of banks installed, and clear the ENADP # bit (enable adapter ROM access).

- Set address range compare registers to top of local memory (at least 1 MByte).

- c. Copy contents of adapter ROM to a temporary buffer in low memory (e.g., 040000h-05FFFFh).

- d. Set the ENADP# bit in the configuration register to enable adapter shadowing.

- e. If 32 Kbyte granularity is desired

- 1. Set EXGRAN = 1.

- Set the shadow bits in the Extended Granularity register that correspond to the address range desired for shadowing.

- Copy contents of temporary buffer to adapter shadow RAM area.

- g. If 32 Kbyte granularity was selected, set the writeprotect bits in the Extended Granularity register that correspond to the address range desired for write-protecting.

Figure 2.5. Shadow RAM Address Map

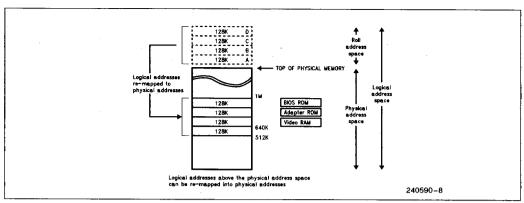

#### 2.3.3 ROLL ADDRESS MAPPING

Roll address mapping is a method of utilizing DRAM memory space that may otherwise not be accessible. The memory space between 640K and 1M (0A0000h-0FFFFFh) is set aside for ROM and system video RAM in AT compatible systems. This space may also be associated with DRAM memory (e.g., one bank of 1M DRAM will reside at the physical address space 0K-2M). The "hidden" DRAM memory that resides in the same address space as the ROM and system video RAM can be either shadowed or it can be "rolled". Address rolling refers to re-mapping one address space to another.

The 82335 SX allows two memory address spaces to be defined; physical and logical. The physical address space corresponds to the amount of DRAM physically connected to the 82335 SX (e.g., one bank of 1M DRAM has the physical address space 0M-2M). The logical address space is the address range that the microprocessor sees as usable. The 82335 SX allows the logical address space to be larger than the physical address space. This is done by remapping logical addresses from above the physical address space (the "roll address" region) into the physical address space hidden by the ROM and video RAM areas. The physical memory between 512K and 640K may also be roll addressed when a 512K base memory is selected. Figure 2.6 illustrates address rolling from a logical to a physical address.

The amount of logical memory that can be rolled is dependent upon the amount of physical memory installed, the base memory selected and the shadow options selected. Up to 512K logical address space can be rolled into physical addresses in 128 Kbyte blocks. At least one megabyte of physical memory must be installed to utilize roll addressing.

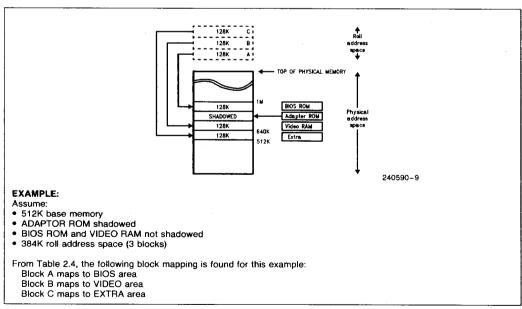

Four physical DRAM areas can be utilized by roll addressing. These are called the BIOS ROM (0E0000h-0FFFFh), ADAPTOR ROM (0C0000h-0DFFFFh), VIDEO RAM (0A0000h-0BFFFFh), and EXTRA (08000h-09FFFFh) areas. The BIOS ROM, ADAPTOR ROM, and VIDEO RAM areas can be selected for roll addressing if they are not selected for shadowing (configuration register bits ROMEN#, ENADP#, and ENV# = 0). The EXTRA area can be selected for roll addressing if a base memory of 512K is selected (memory configuration register bit S640 = 0). Each area can be selected independently of the others.

Figure 2,6. Roll Address Mapping Range

The number of DRAM areas selected for roll addressing determine the size of the roll address space. The address range for this roll address space is programmed via the roll compare registers. The roll address space must be programmed to start on a 512K boundary above the top of the physical address space. It can be programmed such that there is a gap between the physical memory connected to the 82335 SX and the roll address space (e.g., to accommodate add-in memory boards). See Section 2.3.4.2 for details on roll compare register programming.

Memory locations addressed in the roll address space do not map linearly into physical memory locations. Which roll address block maps to which physical memory block is controlled by the shadow and base memory options selected and the number of 128K byte blocks in the roll address space. Table 2.4 indicates how the roll address space maps into the physical address space for the various shadow and memory configurations available.

Figure 2.7 is an example illustrating how roll address blocks map into physical memory blocks.

Figure 2.7. Roll Address Block Mapping Example

| Blocks Not<br>Shadowed         | # of<br>Blocks<br>Rolled | Or                               | der of Logica<br>Blocks Rolle<br>lysical Memo | I Memory           |      |

|--------------------------------|--------------------------|----------------------------------|-----------------------------------------------|--------------------|------|

|                                | 7,0,,,,                  | A                                | В                                             | С                  | D    |

| EXTRA                          | 1                        | EXTRA                            |                                               |                    |      |

| VIDEO                          | 1                        | VIDEO                            |                                               |                    |      |

| ADAPTER                        | 1                        | ADAPTER                          |                                               |                    |      |

| BIOS                           | 1                        | BIOS                             |                                               |                    |      |

| EXTRA, VIDEO                   | 1<br>2                   | VIDEO<br>VIDEO                   | EXTRA                                         |                    |      |

| EXTRA, ADAPTER                 | 1<br>2                   | ADAPTER<br>ADAPTER               | EXTRA                                         |                    |      |

| EXTRA, BIOS                    | 1<br>2                   | BIOS<br>BIOS                     | EXTRA                                         |                    |      |

| VIDEO, ADAPTER                 | 1<br>2                   | ADAPTER<br>ADAPTER               | VIDEO                                         |                    |      |

| ADAPTER, BIOS                  | 1<br>2                   | BIOS<br>BIOS                     | ADAPTER                                       |                    |      |

| VIDEO, BIOS                    | 1 2                      | BIOS<br>BIOS                     | VIDEO                                         |                    |      |

| EXTRA, VIDEO,<br>ADAPTER       | 1<br>2<br>3              | ADAPTER<br>ADAPTER<br>ADAPTER    | VIDEO<br>VIDEO                                | EXTRA              |      |

| EXTRA, ADAPTER,<br>BIOS        | 1<br>2<br>3              | BIOS<br>BIOS<br>BIOS             | ADAPTER<br>ADAPTER                            | EXTRA              |      |

| EXTRA, VIDEO,<br>BIOS          | 1<br>2<br>3              | BIOS<br>BIOS<br>BIOS             | VIDEO<br>VIDEO                                | EXTRA              |      |

| VIDEO, ADAPTER,<br>BIOS        | 1<br>2<br>3              | BIOS<br>BIOS<br>BIOS             | VIDEO<br>VIDEO                                | ADAPTER            |      |

| EXTRA, VIDEO,<br>ADAPTER, BIOS | 1<br>2<br>3<br>4         | EXTRA<br>EXTRA<br>EXTRA<br>EXTRA | VIDEO<br>VIDEO<br>VIDEO                       | ADAPTER<br>ADAPTER | BIOS |

#### LEGEND:

Physical Memory Block Addresses BIOS AREA = 0E0000h-0FFFFh ADAPTER AREA = 0C000h-0DFFFh VIDEO AREA = 0A0000h-0BFFFh EXTRA AREA = 080000h-09FFFh

Logical Memory Block Order

Area A = lowest roll address memory block Area D = highest roll address memory block

<sup>\*</sup>Figure 2.6 illustrates logical memory block order

#### 2.3.4 REGISTERS

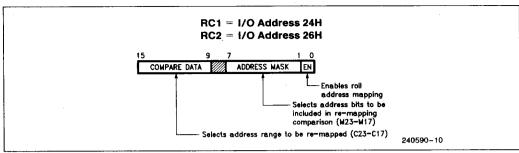

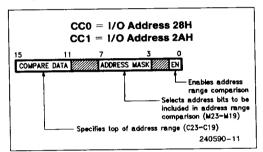

There are seven registers in the 82335 SX that control the operation of the address mapping and DRAM control options. These registers are the configuration, roll compare (RC1 and RC2), address range compare (CC0 and CC1), granularity enable, and extended granularity registers. Each of these registers reside in the local I/O space of the 82335 SX and are read/writable until the LOCK bit has been set in the configuration register. The contents and purpose of each register are described in the following sections.

The 82335 SX contains a one-bit parity check enable register (PARCHEN). This register is a write only register and is not affected by the status of the LOCK bit in the configuration register. See the Parity Generator/Checker section for details on this register.

#### 2.3.4.1 Memory Configuration Register

The memory configuration register resides at I/O location 22H upon system reset and is used to select a number of address mapping and DRAM control options. Upon reset, all bits in this register are set to zero. Figure 2.8 shows the bits used in the memory configuration register. The purpose of each bit is described in the following paragraphs.

ROMEN#: This bit is used to enable or disable shadowing of the BIOS ROM/EPROM in the address range 0E0000H-0FFFFH. When this bit is cleared, BIOS ROM shadowing is disabled. A memory read in this range will access ROM by asserting ROMCSO# or ROMCS1# and by deactivating the OBMEM output. If BIOS ROM shadowing is disabled, this memory space can be accessed via roll addressing. See roll address mapping (Section 2.3.3) for details on address re-mapping.

|      |                 | Memor | y Con | figurat | tion Reg | ister | = 1/0 | Addr | ess 22l | Н     |   | • | _       |

|------|-----------------|-------|-------|---------|----------|-------|-------|------|---------|-------|---|---|---------|

| 15   | 14-12           | 11    | 10    | 9       | 8        | 7     | 6     | 5    | 4       | 3     | 2 | 1 | 0       |

| LOCK |                 | VRO   | ENV#  | ENADP#  | ROMSIZE  | INT   | ERL   |      | DSIZE   | \$640 |   | 1 | ROMEN # |

|      |                 |       |       |         |          |       |       |      |         |       |   |   |         |

|      | Bit<br>Position | Name  |       |         |          |       | Funct | tion |         |       |   |   |         |

| Bit<br>Position | Name    | Function                                                                                                                                                 |

|-----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | ROMEN#  | 0 = Enable BIOS ROM/EPROM Accesses (0E0000H-0FFFFH)<br>1 = Disable BIOS ROM/EPROM Accesses, Shadow Enabled                                               |

| 3               | S640    | 0 = Base Memory Size is 512K<br>1 = Base Memory Size is 640K                                                                                             |

| 4               | DSIZE   | 0 = 256K DRAM Installed<br>1 = 1 Mb DRAM Installed                                                                                                       |

| 7, 6            | INTERL  | 00 = 1 Mem. Bank Installed (Note 1)<br>01 = 2 Mem. Bank installed (Note 1)<br>10 = 2 Mem. Bank Installed (Note 1)<br>11 = 4 Mem. Bank Installed (Note 1) |

| 8               | ROMSIZE | 0 = 256K ROM/EPROM<br>1 = 512K ROM/EPROM                                                                                                                 |

| 9               | ENADP#  | 0 = Enable Adaptor ROM/EPROM Accesses (0C0000H-0DFFFFH)<br>1 = Disable Adaptor ROM/EPROM Accesses, Shadow Enabled                                        |

| 10              | ENV#    | 0 = Enable Video RAM Accesses (0A0000H-0BFFFFH) (Note 2)<br>1 = Disable Video RAM Accesses, Shadow Enabled                                               |

| 11              | VRO     | Video Read Only 0 = Video Area Read-Write (0A0000H-0BFFFFH) 1 = Video Area Read-Only                                                                     |

| 15              | LOCK    | 0 = Enable all Configuration Register Accesses 1 = Disable all Configuration Register Accesses                                                           |

#### NOTES

- 1. When more than one bank of memory is installed, banks are always interleaved.

- 2. For AT compatible operation, Video RAM should be enabled (ENV# = 0).

Figure 2.8. Memory Configuration Register

When this bit is set, and EXGRAN and the extended granularity register is set appropriately, BIOS ROM shadowing is enabled and memory accesses to this address range are made from local DRAM. During shadow DRAM accesses, the OBMEM signal is asserted and the ROMCSO# and ROMCS1# signals are disabled.

S640: This bit selects the base memory size. When cleared, a base memory of 512K is selected. When set, a base memory of 640K is selected. If a base memory of 512K is selected, the address range 080000H-09FFFFH can be accessed via roll addressing. See roll address mapping (Section 2.3.3) for details on address re-mapping.

**DSIZE:** This bit is used to indicate the type of DRAM installed. When cleared, it indicates 256K DRAM and when set, it indicates 1M DRAM installed. DRAM sizes cannot be mixed. When 256K DRAM is installed, the multiplexed address line MA9 is not used.

INTERL: These two bits indicate the number of banks of memory installed. When more than one memory bank is installed, the banks are always interleaved. If the INTERL bits are set for one memory bank, RAS and CAS signals are generated for bank 0. If set to two bank operation, RAS and CAS signals are generated for banks 0 and 1. If set to four bank operation, RAS and CAS signals are generated for banks 0 and 1. The 82335 SX does not allow 3 way interleaving. Therefore if the INTERL bits are set to three, the 82335 SX will default to 2 bank operation, i.e., RAS and CAS will be generated for banks 0 and 1 only.

ROMSIZE: This bit indicates the size of the installed ROM/EPROM. When cleared, it indicates 256K bit ROM/EPROM and when set, it indicates 512K bit ROM/EPROM is installed. This bit also affects the ROMCS0 # and ROMCS1 # address decode ranges when ROM shadowing is disabled. See Chip Select Signals (Section 2.3.5) for further information.

ENADP#: This bit is used to enable or disable shadowing of the adapter ROM area. If cleared, adapter ROM shadowing is disabled and accesses to the memory range 0C0000H-0DFFFFH will be made from ROM. When this bit is set and EXGRAN and the extended granularity register is set appropriately, adapter ROM shadowing is enabled and memory accesses in this range will be from local DRAM. If adapter ROM shadowing is disabled, this memory space can be accessed via roll addressing. See roll address mapping (Section 2.3.3) for details on address re-mapping.

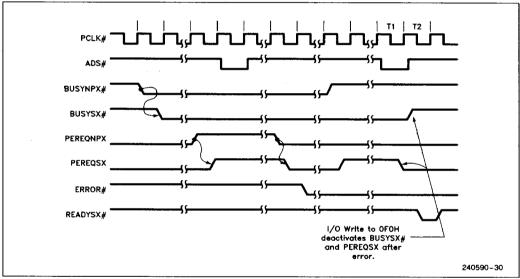

ENV#: This bit is used to enable or disable shadowing of the external video RAM. If cleared, video RAM shadowing is disabled and accesses to the memory range 0A0000H-0BFFFFH will be made to/from the system video RAM. If set, video RAM shadowing is enabled and memory accesses in this range will be to/from local DRAM. For AT compatible operation, video RAM shadowing should be disabled (ENV# = 0). If video RAM shadowing is disabled, this memory space can be accessed via roll addressing. See roll address mapping (Section 2.3.3) for details on address re-mapping.