### **Distinctive Characteristics**

- Fully parallel, 8-bit data register and buffer replacing latches, multiplexers and buffers needed in microprocessor systems.

- 4.0V output high voltage for direct interface to MOS microprocessors, such as the Am9080A family.

- Input load current 250µA max.

- Reduces system package count

ACTIVE LOW

- Available for operation over both commercial and military temperature ranges.

- Service request flip-flop for interrupt generation

- Three-state outputs sink 15mA

- Asynchronous register clear with clock over-ride

ORDERING INFORMATION

Temperature

Range

-55°C to +125°C

0°C to +70°C

$0^{\circ}C$  to  $+70^{\circ}C$

0°C to +70°C

11

Order

Number

AM8212DM

D8212

P8212

AM8212XC

Package

Турє

Hermetic DIP

Hermetic DIP Molded DIP

Dice

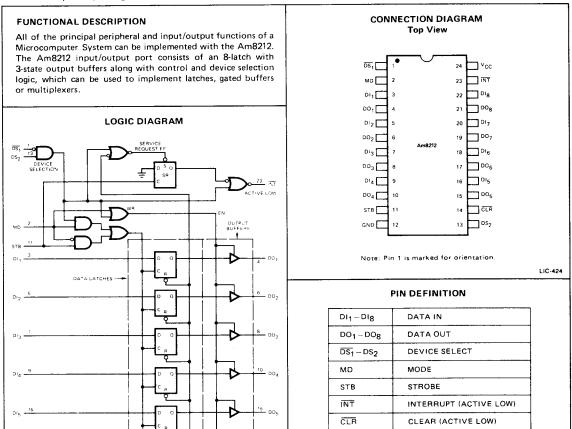

### FUNCTIONAL DESCRIPTION (Cont'd)

#### Data Latch

The 8 flip-flops that make up the data latch are of a "D" type design. The output (Q) of the flip-flop will follow the data input (D) while the clock input (C) is high. Latching will occur when the clock (C) returns low.

The data latch is cleared by an asynchronous reset input  $(\overline{CLR})$ . (Note: Clock (C) Overrides Reset  $(\overline{CLR})$ ).

#### Output Buffer

The outputs of the data latch (Q) are connected to 3-state, non-inverting output buffers. These buffers have a common control line (EN); this control line either enables the buffer to transmit the data from the outputs of the data latch (Q) or disables the buffer, forcing the output into a high impedance state. (3-state). This high-impedance state allows the Am8212 to be connected directly onto the microprocessor bidirectional data bus.

### Control Logic

The Am8212 has control inputs  $\overline{DS}_1$ ,  $DS_2$ , MD and STB. These inputs are used to control device selection, data latching, output buffer state and service request flip-flop.

### DS1, DS2 (Device Select)

These 2 inputs are used for device selection. When  $\overline{DS}_1$  is low and  $DS_2$  is high  $(\overline{DS}_1 \cdot DS_2)$  the device is selected. In the selected state the output buffer is enabled and the service request flip-flop (SR) is asynchronously set.

### MD (Mode)

This input is used to control the state of the output buffer and to determine the source of the clock input (C) to the data latch

When MD is high (output mode) the output buffers are enabled and the source of clock (C) to the data latch is from the device selection logic ( $\overline{DS}_1 \cdot DS_2$ ).

When MD is low (input mode) the output buffer state is determined by the device selection logic  $(\overline{DS}_1 \cdot DS_2)$  and the source of clock (C) to the data latch is the STB (Strobe) input.

#### STB (Strobe)

This input is used as the clock (C) to the data latch for the input mode MD = 0) and to synchronously reset the service request flip-flop (SR).

Note that the SR flip-flop is negative edge triggered.

### Service Request Flip-Flop

The SR flip-flop is used to generate and control interrupts in microcomputer systems. It is asynchronously set by the  $\overline{\text{CLR}}$  input (active low). When the (SR) flip-flop is set it is in the non-interrupting state.

The output of the (SR) flip-flop (Q) is connected to an inverting input of a "NOR" gate. The other input to the "NOR" gate is non-inverting and is connected to the device selection logic ( $\overline{\rm DS}_1$  · DS<sub>2</sub>). The output of the "NOR" gate ( $\overline{\rm INT}$ ) is active low (interrupting state) for connection to active low input priority generating circuits.

## TRUTH TABLE

| STB | MD | DS <sub>1</sub> - DS <sub>2</sub> | Data Out Equa |  |

|-----|----|-----------------------------------|---------------|--|

| 0   | 0  | 0                                 | Three-State   |  |

| 1   | 0  | 0                                 | Three-State   |  |

| 0   | 1  | 0                                 | Data Latch    |  |

| 1   | 1  | 0                                 | Data Latch    |  |

| 0   | 0  | 1                                 | Data Latch    |  |

| 1   | 0  | 1                                 | Data In       |  |

| 0   | 1  | 1                                 | Data In       |  |

| 1   | 1  | 1                                 | Data In       |  |

| CLR | $\overline{DS_1} - DS_2$ | STB | SR* | INT |

|-----|--------------------------|-----|-----|-----|

| 0   | 0                        | 0   | 1   | 1   |

| 0   | 1                        | 0   | 1   | 0   |

| 1   | 1                        | ~   | 0   | 0   |

| 1   | 1                        | 0   | 1   | 0   |

| 1   | 0                        | 0   | 1   | 1   |

| 1   | 1                        | 7   | 1   | 0   |

|     |                          |     |     |     |

|     |                          |     |     |     |

CLR - Resets Data Latch

Sets SR Flip-Flop (no effect on Output Buffer)

\* Internal SR Flip-Flop

# MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature              | −65°C to +150°C |

|----------------------------------|-----------------|

| Temperature (Ambient) Under Bias | –55°C to +125°C |

| Supply Voltage                   | -0.5V to +7.0V  |

| Output Voltage                   | -0.5V to +7.0V  |

| Input Voltages                   | -1.0V to +5.5V  |

| Output Current (Each Output)     | 125mA           |

# ELECTRICAL CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (Unless Otherwise Noted)

P8212, D8212 (COM'L) Am8212DM (MIL)

$T_A = 0^{\circ} C \text{ to } +70^{\circ} C$  $T_A = -55^{\circ}C \text{ to } +125^{\circ}C$

$V_{CC} = 5.0V \pm 5\%$ V<sub>CC</sub> = 5.0V ± 10%

# DC CHARACTERISTICS

| arameters                                                                   | Description                                                                               | Test Conditions                |       | Min. | Typ.<br>(Note 1) | Max.  | Units |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|-------|------|------------------|-------|-------|

| 1 <sub>F</sub>                                                              | Input Load Current<br>ACK, DS <sub>2</sub> , CR, DI <sub>1</sub> - DI <sub>8</sub> Inputs | V <sub>F</sub> = 0.45V         |       |      |                  | -0.25 | mA    |

| 1F                                                                          | Input Load Current MD Input                                                               | V <sub>F</sub> = 0.45V         |       |      |                  | -0.75 | mA    |

| le l                                                                        | Input Load Current DS <sub>1</sub> Input                                                  | VF = 0.45V                     |       |      |                  | -1.0  | mA    |

| Input Leakage Current ACK, DS, CR, DI <sub>1</sub> – DI <sub>8</sub> Inputs |                                                                                           | V <sub>R</sub> = 5.25V         |       |      |                  | 10    | μА    |

| IR                                                                          | Input Leakage Current MO Input                                                            | ge Current MO Input VR = 5.25V |       |      |                  | 30    | μΑ    |

| I <sub>R</sub>                                                              | Input Leakage Current DS <sub>1</sub> Input                                               | V <sub>R</sub> = 5.25V         |       |      |                  | 40    | μА    |

|                                                                             | Input Forward Voltage Clamp                                                               | I <sub>C</sub> = -5.0mA        | COM'L |      |                  | -1.0  | Volts |

| V <sub>C</sub>                                                              |                                                                                           |                                | MIL.  |      |                  | -1.2  |       |

| ***                                                                         |                                                                                           |                                | COM'L |      | T                | 0.85  | Volts |

| VIL                                                                         | Input LOW Voltage                                                                         |                                | MIL   |      |                  | 0.80  | Voits |

| VIH                                                                         | Input HIGH Voltage                                                                        |                                |       | 2.0  |                  |       | Volts |

| VOL                                                                         | Output LOW Voltage                                                                        | IOL = 15mA                     |       |      |                  | 0.45  | Volts |

|                                                                             |                                                                                           | I <sub>OH</sub> = -1.0mA       | COM'L | 3.65 | 4.0              |       | Volts |

|                                                                             | Output HIGH Voltage                                                                       |                                | MIL   | 3.3  | 4.0              |       |       |

|                                                                             |                                                                                           | I <sub>OH</sub> = -0.5mA       | MIL   | 3.4  | 4.0              |       |       |

| 1 <sub>SC</sub>                                                             | Short Circuit Output Current                                                              | V <sub>O</sub> = 0V            |       | -15  |                  | -75   | mA    |

| liol                                                                        | Output Leakage Current<br>High Impedance                                                  | V <sub>O</sub> = 0.45V/5.25V   |       |      |                  | 20    | μА    |

| Icc                                                                         | Power Supply Current                                                                      | Note 2                         |       |      | 90               | 130   | mA    |

### O OUADAOTEDICTICS (N

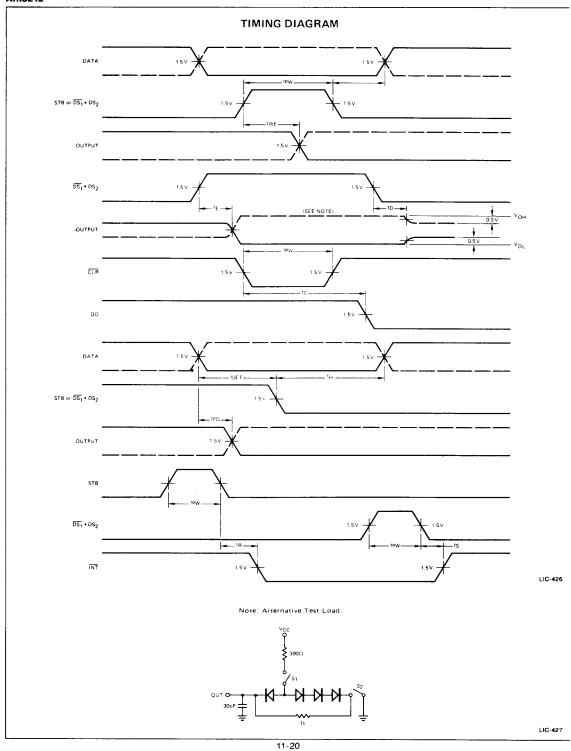

| TERISTICS (Note 3)  Description | Min.                                                                                                                                                                                   | Typ.<br>(Note 1)                                                                                                                                                                                                                                                                                                 | Max.                                                                                                                                                                                                                                                                                                                                                                                           | Units                                                                                                                                                                                                                                                     |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse Width                     | 30                                                                                                                                                                                     | 8                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                        |

| Data to Output Delay            |                                                                                                                                                                                        | 12                                                                                                                                                                                                                                                                                                               | 30                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                        |

| Write Enable to Output Delay    |                                                                                                                                                                                        | 18                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                        |

| Data Set-up Time                | 15                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                        |

| Data Hold Time                  | 20                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                        |

| Reset to Output Delay           |                                                                                                                                                                                        | 18                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                        |

| Set to Output Delay             |                                                                                                                                                                                        | 15                                                                                                                                                                                                                                                                                                               | 30                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                        |

| Output Enable/Disable Time      |                                                                                                                                                                                        | 14                                                                                                                                                                                                                                                                                                               | 45                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                        |

| Clear to Output Delay           |                                                                                                                                                                                        | 25                                                                                                                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                        |

|                                 | Description  Pulse Width  Data to Output Delay  Write Enable to Output Delay  Data Set-up Time  Data Hold Time  Reset to Output Delay  Set to Output Delay  Output Enable/Disable Time | Description         Min.           Pulse Width         30           Data to Output Delay            Write Enable to Output Delay            Data Set-up Time         15           Data Hold Time         20           Reset to Output Delay            Set to Output Delay            Output Enable/Disable Time | Description         Min.         (Note 1)           Pulse Width         30         8           Data to Output Delay         12           Write Enable to Output Delay         18           Data Set-up Time         15           Data Hold Time         20           Reset to Output Delay         18           Set to Output Delay         15           Output Enable/Disable Time         14 | Description         Min.         (Note 1)         Max.           Pulse Width         30         8           Data to Output Delay         12         30           Write Enable to Output Delay         18         40           Data Set-up Time         15 |

# CAPACITANCE (Note 4)

$F = 1.0 MHz, V_{BIAS} = 2.5 V, V_{CC} = +5.0 V, T_{A} = 25^{\circ}C$

| arameters | Description                                                                       | Тур. | Max. | Units |  |

|-----------|-----------------------------------------------------------------------------------|------|------|-------|--|

| CIN       | DS <sub>1</sub> MD Input Capacitance                                              | 9.0  | 12   | pF    |  |

| CIN       | DS <sub>2</sub> , CK, ACK, DI <sub>1</sub> – DI <sub>8</sub><br>Input Capacitance | 5.0  | 9.0  | pF    |  |

| COUT      | DO <sub>1</sub> – DO <sub>8</sub> Output Capacitance                              | 8.0  | 12   | рF    |  |

- Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. CLR = STB = HIGH; DS<sub>1</sub> = DS<sub>2</sub> = MD = LOW; all data inputs are gound, all data outputs are open.

3. Conditions of Test: a) Input pulse amplitude = 2.5V

- - b) Input rise and fall times 5.0ns

c) Between 1.0V and 2.0V measurements made at 1.5V with 15mA and 30pF Test Load.

4. This parameter is sampled and not 100% tested.

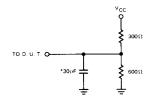

TEST LOAD (15mA and 30pF)

\*Including Jig and Probe Capacitance. LIC-425

11-19

Powered by ICminer.com Electronic-Library Service CopyRight 2003

11

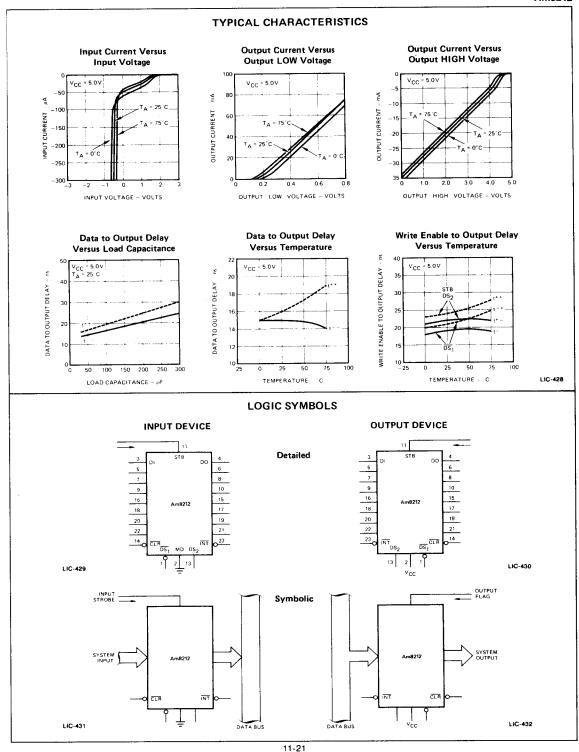

### **TYPICAL APPLICATIONS OF THE Am8212**

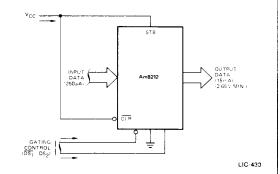

### **GATED BUFFER (3-STATE)**

By tying the mode signal low and the strobe input high, the data latch is acting as a straight through gate. The output buffers are then enabled from the device selection logic  $\overline{\text{DS}}_1$  and  $\text{DS}_2$ .

When the device selection logic is false, the outputs are 3-state.

When the device selection logic is true, the input data from the system is directly transferred to the output.

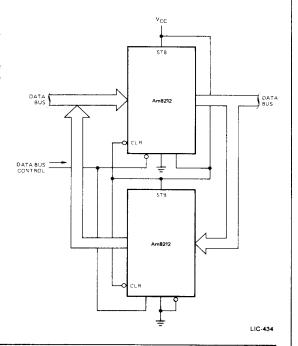

### Bi-Directional Bus Driver

Two Am8212s wired back to back can be used as a symmetrical drive, bi-directional bus driver. The devices are controlled by the data bus input control which is connected to  $\overline{\text{DS}_1}$  on the first Am8212 and to  $\text{DS}_2$  on the second. While one device is active, and acting as a straight through buffer the other is in its 3-state mode.

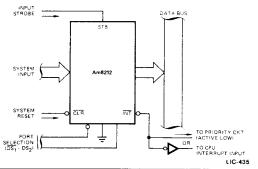

### Interrupting Input Port

The Am8212 accepts a strobe from the system input source, which in turn clears the service request flip-flop and interrupts the processor. The processor then goes through a service routine, identifies the port, and causes the device selection logic to go true—enabling the system input data onto the data bus.

11-22

# TYPICAL APPLICATIONS OF THE Am8212 (Cont'd)

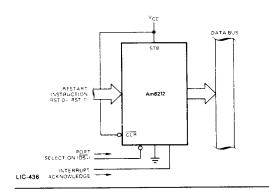

### Interrupt Instruction Port

The Am8212 can be used to gate the interrupt instruction, normally RESTART instructions, onto the data bus. The device is enabled from the interrupt acknowledge signal from the microprocessor and from a port selection signal. This signal is normally tied to ground.  $(\overline{DS_1}$  could be used to multiplex a variety of interrupt instruction ports onto a common bus.)

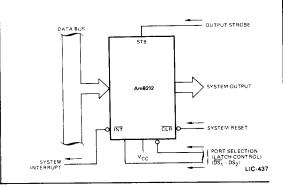

### Output Port (With Hand-Shaking)

The Am8212 is used to transmit data from the data bus to a system output. The output strobe could be a hand-shaking signal such as "reception of data" from the device that the system is outputting to. It in turn, can interrupt the system signifying the reception of data. The selection of the port comes from the device selection logic. ( $\overline{\text{DS}_1} - \text{DS}_2$ .)

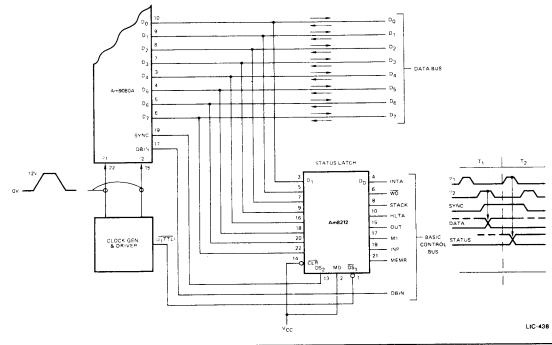

### Ami9080A Status Latch

The input to the Am8212 latch comes directly from the Am9080A data bus. Timing shows that when the SYNC signal is true  $(\overline{DS}_1$  input), and  $\wp1$  is true,  $(\overline{DS}_1$  input) then the

status data will be latched into the Am8212. The mode signal is tied high so that the output on the latch is active and enabled all the time.

11