# **NEC Microcomputers, Inc.**

**ДРВ8214**

## PRIORITY INTERRUPT CONTROLLER

## **DESCRIPTION**

The  $\mu$ PB8214 is an eight-level priority interrupt controller. Designed to simplify interrupt driven microcomputer systems, the  $\mu$ PB8214 requires a single +5V power supply and is packaged in a 24 pin plastic Dual-in-line package.

The µPB8214 accepts up to eight interrupts, determines which has the highest priority and then compares that priority with a software created current status register. If the incoming requires is of a higher priority than the interrupt currently being serviced, an interrupt request to the processor is generated. Vector information that identifies the interrupting device is also generated.

The interrupt structure of the microcomputer system can be expanded beyond eight interrupt levels by cascading  $\mu$ PB8214s. The  $\mu$ PB8214's interrupt and vector information outputs are open collector and control signals are provided to simplify expansion of the interrupt structure.

## **FEATURES**

- · Eight Priority Levels

- Current Status Register and Priority Comparator

- Easily Expanded Interrupt Structure

- Single +5 Volt Supply

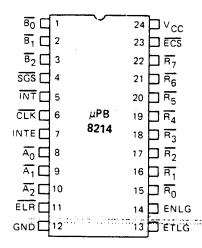

## PIN CONFIGURATION

## **PIN NAMES**

| Inputs                            |                        |                |

|-----------------------------------|------------------------|----------------|

| $\overline{R_0}$ $\overline{R_7}$ | Request Levels IR 7 Hi | ghesi Primary) |

| B <sub>0</sub> B <sub>1</sub> ,   | Current Status         |                |

| SGS                               | Status Group Select    |                |

| ĒČŠ                               | Enable Current Status  |                |

| INTE                              | Interrupt Enable       |                |

| ĈĹΚ                               | Clock (INT F.E)        |                |

| ΕίR                               | Enable Level Read      |                |

| ETLG                              | Enable This Level Gro  | up             |

| Outputs                           |                        |                |

| Ā <sub>0</sub> Ä <sub>2</sub>     | Request Levels         | Open           |

| tNT                               | Interrupt (Act Low)    | Collector      |

| ENLG                              | Enoble Next Level Gro  | up             |

## μPB8214

#### General

The  $\mu$ PB8214 is an LSI device designed to simplify the circuitry required to implement an interrupt driven microcomputer system. Up to eight interrupting devices can be connected to a  $\mu$ PB8214, which will assign priority to incoming interrupt requests and accept the highest. It will also compare the priority of the highest incoming request with the priority of the interrupt being serviced. If the serviced interrupt has a higher priority, the incoming request will not be accepted.

A system with more than eight interrupting devices can be implemented by interconnecting additional  $\mu$ PB8214s. In order to facilitate this expansion, control signals are provided for cascading the controllers so that there is a priority established among the controllers. In addition, the interrupt and vector information outputs are open collector.

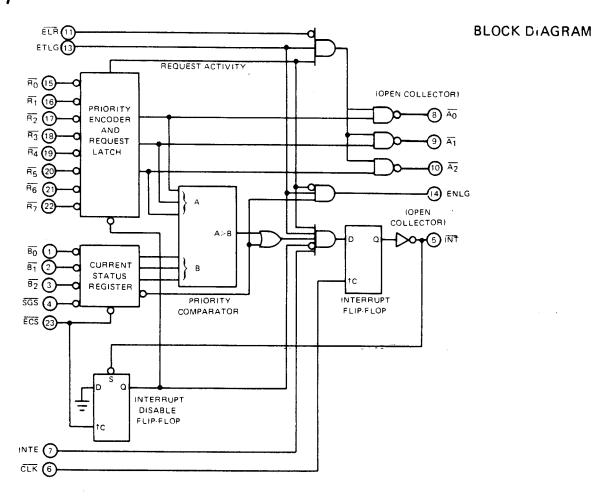

## Priority Encoder and Request Latch

The priority encoder portion of the  $\mu$ PB8214 accepts up to eight active low interrupt requests ( $R_0-R_7$ ). The circuit assigns priority to the incoming requests, with  $R_7$  having the highest priority and  $R_0$  the lowest. If two or more requests occur simultaneously, the  $\mu$ PB8214 accepts the one having the highest priority. Once an incoming interrupt request is accepted, it is stored by the request latch and a three-bit code is output. As shown in the following table, the outputs, ( $\overline{A_0}-\overline{A_2}$ ) are the complement of the request level (modulo 8) and directly correspond to the bit pattern required to generate the one byte RESTART (RST) instructions recognized by an 8080A. Simultaneously with the  $\overline{A_0}-\overline{A_2}$  outputs, a system interrupt request ( $\overline{INT}$ ) is output by the  $\mu$ PB8214. It should be noted that incoming interrupt requests that are *not* accepted are not latched and must remain as an input to the  $\mu$ PB8214 in order to be serviced.

E-Z

FUNCTIONAL DESCRIPTION

## FUNCTIONAL DESCRIPTION (CONT.)

|     | RESTART GENERATION TABLE |                |     |                |                |                  |                |                |                |                |                |

|-----|--------------------------|----------------|-----|----------------|----------------|------------------|----------------|----------------|----------------|----------------|----------------|

|     |                          |                |     | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub>   | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|     | PRIORIT<br>REQUES        |                | RST | 1              | 1              | $\overline{A_2}$ | ĀŢ             | A <sub>0</sub> | 1              | ,              | 1              |

|     | LOWEST                   | R <sub>0</sub> | 7   | 1              | 1              | ,                | 1              | 1              | 1              | 1              | 1              |

| -   |                          | R <sub>1</sub> | 6   | 1              | 1              | 1                | 1              | 0              | 1              | 1              | 1              |

| - 1 |                          | R <sub>2</sub> | 5   | 1              | 1              | 1                | 0              | 1              | 1              | 1              | 1              |

|     |                          | R <sub>3</sub> | 4   | . 1            | 1              | 1                | 0              | 0              | 1              | 1              | . 1            |

|     |                          | R <sub>4</sub> | 3   | 1              | 1              | 0                | 1              | 1              | 1              | 1              | 1              |

| ļ   |                          | Ŕ <sub>5</sub> | 2   | 1              | T              | 0                | 1              | 0              | 1              | 1              | 1              |

|     | ŧ                        | R <sub>6</sub> | 1   | 1              | 1              | 0                | 0              | 1              | 1              | 1. 1           | 1              |

|     | HIGHEST                  | R <sub>7</sub> | 0.  | 1              | 1              | 0                | 0              | 0              | 1              | 1              | 1              |

"CAUTION RST 0 will vector the program counter to location 0 (zero) and invoke the same routine as the "RESET" input to 8080A.

#### **Current Status Register**

The current status register is designed to prevent an incoming interrupt request from overriding the servicing of an interrupt with higher priority. Via software, the priority level of the interrupt being serviced by the microprocessor is written into the current status register on  $\overline{B_0}$ — $\overline{B_2}$ . The bit pattern written should be the complement of the interrupt level.

The interrupt level currently being serviced is written into the current status register by driving  $\overline{ECS}$  (Enable Current Status) low. The  $\mu$ PB8214 will only accept interrupts with a higher priority than the value contained by the current status register. Note that the programmer is free to use the current status register for other than as above. Other levels may be written into it. The comparison may be completely disabled by driving  $\overline{SGS}$  (Status Group Select) low when  $\overline{ECS}$  is driven low. This will cause the  $\mu$ PB8214 to accept incoming interrupts only on the basis of their priority to each other.

## **Priority Comparator**

The priority comparator circuitry compares the level of the interrupt accepted by the priority encoder and request latch with the contents of the current status register. If the incoming request has a priority level higher than that of the current status register, the  $\overline{\text{INT}}$  output is enabled. Note that this comparison can be disabled by loading the current status register with  $\overline{\text{SGS}}$ =0.

## **Expansion Control Signals**

A microcomputer design may often require more than eight different interrupts. The  $\mu$ PB8214 is designed so that interrupt system expansion is easily performed via the use of three signals: ETLG (Enable This Level Group); ENLG (Enable Next Level Group); and  $\overline{\text{ELR}}$  (Enable Level Read). A high input to ETLG indicates that the  $\mu$ PB8214 may accept an interrupt. In a typical system, the ENLG output from one  $\mu$ PB8214 is connected to the ETLG input of another  $\mu$ PB8214, etc. The ETLG of the  $\mu$ PB8214 with the highest priority is tied high: This configuration sets up priority among the cascaded  $\mu$ PB8214's. The ENLG output will be high for any device that does not have an interrupt pending, thereby allowing a device with lower priority to accept interrupts. The  $\overline{\text{ELR}}$  input is basically a chip enable and allows hardware or software to selectively disable/enable individual  $\mu$ PB8214's. A low on the  $\overline{\text{ELR}}$  input enables the device.

## μPB8214

#### Interrupt Control Circuitry

02 Dã

The µPB8214 contains two flip-flops and several gates which determine whether an accepted interrupt request to the  $\mu$ PB8214 will generate a system interrupt to the 8080A. A condition gate drives the D input of the interrupt flip-flop whenever an interrupt request has been completely accepted. This requires that: the ETLG (Enable This Level Group) and INTE (Interrupt Enable) inputs to the  $\mu$ PB8214 are high; the ELR input is low; the incoming request must be of a higher priority than the contents of the current status register; and the µPB8214 must have been enabled to accept interrupt requests by the clearing of the interrupt disable flip-flop.

Once the condition gate drives the D input of the interrupt flip-flop high, a system interrupt (INT) to the 8080A is generated on the next rising edge of the CLK input to the  $\mu$ PB8214. This  $\overline{CLK}$  input is typically connected to the  $\phi$ 2 (TTL) output of an 8224 so that 8080A set-up time specifications are met. When INT is generated, it sets the interrupt disable flip-flop so that no additional system interrupts will be generated until it is reset. It is reset by driving ECS (Enable Current Status) low. thereby writing into the current status register.

It should be noted that the open collector  $\overline{INT}$  output from the  $\mu PB8214$  is active for only one clock period and thus must be externally latched for inputting to the 8080A. Also, because the  $\overline{\text{INT}}$  output is open collector, when  $\mu\text{PB8214's}$  are cascaded, an INT output from any one will set all of the interrupt disable flipflops in the array. Each µPB8214's interrupt disable flip-flop must then be cleared individually in order to generate subsequent system interrupts.

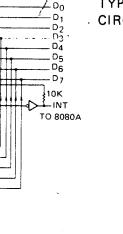

8080A DATA BUS

**FUNCTIONAL** DESCRIPTION (CONT.)

TYPICAL µPB8214 **CIRCUITRY**

```

D4

D_5

D<sub>6</sub>

0

INTE

DOO

R

DO<sub>1</sub>

-8

DO<sub>2</sub>

10

INTERRUPT

R<sub>3</sub>

\bar{A_0}

DO3

μPB DO4

REQUESTS

Ã1

20

18 D5

10

8212<sub>DO5</sub>

A<sub>2</sub>

20 D6

DO<sub>6</sub>

R<sub>6</sub>

μPB

8214

13

CLR

ETLG

DS2 MD DS1

81

8 7

GND

NTA

SGS

ENABLE

ECS

CURRENT

STATUS

(FROM I/O PORT DECODER)

```

All Output and Supply Voltages .....-0.5 to +7 Volts Output Currents ...... 100 mA

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$T_a = 25^{\circ}C$

ABSOLUTE MAXIMUM **RATINGS\***

DC CHARACTERISTICS  $T_a = 0^{\circ}C$  to +70°C,  $V_{CC} = 5V \pm 5\%$

| PARAMETER                                 | CV44DOL |      | LIMITS |       |      | TERT CONDITIONS  |

|-------------------------------------------|---------|------|--------|-------|------|------------------|

| PANAMETER                                 | SYMBOL  | MIN. | TYP. ① | MAX.  | UNIT | TEST CONDITIONS  |

| Input Clamp Voltage (all inputs)          | ٧c      |      |        | - 1.0 | ٧    | IC≖-5mA          |

| Input Forward Current: ETLG input         | 1F      |      | 15     | -0.5  | mΑ   | VF=0.45V         |

| all other inputs                          |         |      | 08     | -0.25 | mA   |                  |

| Input Reverse Current: ETLG input         | 1R      |      |        | 80    | μΑ   | VR=5.25V         |

| all other inputs                          |         |      |        | 40    | μА   |                  |

| Input LOW Voltage: all inputs             | VIL     |      |        | 0.8   | V    | VCC=5.0V         |

| Input HIGH Voltage: all inputs            | VIH     | 2.0  |        |       | V    | Vcc=5.0V         |

| Power Supply Current                      | 1cc     |      | 90     | 130   | mA   | 2                |

| Output LOW Voltage: all outputs           | VOL     |      | .3     | .45   | V    | IOL=10mA         |

| Output HIGH Voltage: ENLG output          | ∨он     | 2.4  | 3.0    |       | V    | IOH=- 1mA        |

| Short Circuit Output Current: ENLG output | los     | - 20 | - 35   | - 55  | mA   | VOS=0V, VCC=5.0V |

| Output Leakage Current: INT and A0-A2     | ICEX    | ,    |        | 100   | μА   | VCEX=5.25V       |

## CAPACITANCE © T<sub>a</sub> = 25°C

| PARAMETER          | SYMBOL   |      | LIMITS |      | UNIT | TEST CONDITIONS  |

|--------------------|----------|------|--------|------|------|------------------|

| PARAMETER          | STIVIBUL | MIN. | TYP. ① | MAX. | UNIT | TEST CONDITIONS  |

| Input Capacitance  | CIN      |      | 5      | 10   | рF   | VBIAS=2.5V       |

| Output Capacitance | COUT     |      | 7      | 12   | pF   | VCC=5V<br>f=1mHz |

AC CHARACTERISTICS  $T_a = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{CC} = +5V \pm 5\%$

| PARAMETER                                                                          | SYMBOL           |      | LIMITS |      | UNIT | TEST CONDITIONS      |

|------------------------------------------------------------------------------------|------------------|------|--------|------|------|----------------------|

| PARAMETER                                                                          | STWBUL           | MIN. | TYP.①  | MAX. | UNIT | TEST CONDITIONS      |

| CLK Cycle Time                                                                     | tCY              | 80   | 50     |      | ns   | Input pulse          |

| CLK, ECS, INT Pulse Width                                                          | tPW              | 25   | 15     |      | ns   | amplitude: 2.5 Volts |

| INTE Setup Time to CLK                                                             | tiss             | 16   | 12     |      | ns   |                      |

| INTE Hold Time after CLK                                                           | tish             | 20   | - 10   |      | ns   |                      |

| ETLG Setup Time to CLK                                                             | tETCS@           | 25   | 12     |      | ns   | Input rise and fall  |

| ETLG Hold Time After CLK                                                           | tETCH 4          | 20   | 10     |      | ns   | times: 5 ns between  |

| ECS Setup Time to CLK                                                              | tECCS 4          | 80   | 50     |      | ns   | 1 and 2 Volts        |

| ECS Hold Time After CLK                                                            | tECCH 5          | 0    |        |      | ns   |                      |

| ECS Setup Time to CLK                                                              | tECRS 5          | 110  | 70     |      | ns   |                      |

| ECS Hold Time After CLK                                                            | tECRH ®          | 0    |        |      |      | Output loading of    |

| ECS Setup Time to CLK                                                              | ¹ECSS ④          | 75   | 70     |      | ns   | 15 mA and 30 pF      |

| ECS Hold Time After CLK                                                            | tECSH €          | 0    |        |      | ns   |                      |

| SGS and BO-B2 Setup Time to CLK                                                    | tDCS 4           | 70   | 50     |      | ns   |                      |

| SGS and 80-82 Hold Time After CLK                                                  | tDCH ④           | 0    |        |      | ns   | Speed measurement    |

| R <sub>0</sub> -R <sub>7</sub> Setup Time to CLK                                   | TRCS (5)         | 90   | 55     |      | ns   | taken at the 1.5 Vo  |

| R0-R7 Hold Time After CLK                                                          | tRCH®            | 0    |        |      | ns   | levels.              |

| INT Setup Time to CLK                                                              | tics             | 55   | 35     |      | ns   |                      |

| CLK to INT Propagation Delay                                                       | tCI              |      | 15     | 25   | ns   |                      |

| R <sub>0</sub> -R <sub>7</sub> Setup Time to INT                                   | tRIS ®           | 10   | 0      |      | ns   |                      |

| R0-R7 Hold Time After INT                                                          | tRIH®            | 35   | 20     |      | ns   |                      |

| R <sub>0</sub> -R <sub>7</sub> to A <sub>0</sub> -A <sub>2</sub> Propagation Delay | tRA              |      | 80     | 100  | ns   |                      |

| ELR to A <sub>0</sub> -A <sub>2</sub> Propagation Delay                            | tELA             |      | 40     | 55   | ns   |                      |

| ECS to A <sub>0</sub> -A <sub>2</sub> Propagation Delay                            | <sup>t</sup> ECA | ļ    | 100    | 120  | ns   |                      |

| ETLG to A0-A2 Propagation Delay                                                    | ¹ETA             |      | 35     | 70   | ns   | 1                    |

| SGS and B0-B2 Setup Time to ECS                                                    | tDECS ®          | 15   | 10     |      | ns   | 1                    |

| SGS and Bo-B2 Hold Time After ECS                                                  | 1DECH ®          | 15   | 10     |      | ns   | 1                    |

| R <sub>0</sub> -R <sub>7</sub> to ENLG Propagation Delay                           | tREN             |      | 45     | 70   | ris  | 1                    |

| ELTG to ENLG Propagation Delay                                                     | tETEN            |      | 20     | . 25 | ns · | <b> </b>             |

| ECS to ENLG Propagation Delay                                                      | tECRN            |      | 85     | 90   | ns   | 1                    |

| ECS to ENLG Propagation Delay                                                      | tECSN            |      | 35     | 55   | ns   | 1                    |

- Typical values are for  $T_a=25^{\circ}C$ ,  $V_{CC}=5.0V$  $\overline{8_0}-\overline{8_2}$ ,  $\overline{SGS}$ ,  $\overline{CLK}$ ,  $\overline{R_0}-\overline{R_4}$  grounded, all other inputs and all outputs

- This parameter is periodically sampled and not 100% tested.

- Required for proper operation if INTE is enabled during next clock pulse.

- These times are not required for proper operation but for desired change in interrupt flip-flop.

- Required for new request or status to be properly loaded.

VISUAL TECHNOLOGY INCORPORATED, RAILROAD AVENUE, DUNDEE PARK, ANDOVER, MA 01810

Ē0-₹7 †RCS 1RIS <sup>t</sup>RIH ETLG INTE  $\overline{\text{SGS}}, \ \overline{\text{B}_0} \cdot \overline{\text{B}_2}$ †DECS 1DCS <sup>t</sup>ECSS tECSH ĒČŠ <sup>t</sup>ECRS TECRH tpW CLK TECRN tics ĪNT ELR <sup>t</sup>ECA  $\overline{A_0}.\,\overline{A_2}$ ENLG v<sub>cc</sub>  $300\Omega$ OUT .  $600\Omega$ 30 pf

**TIMING WAVEFORMS**

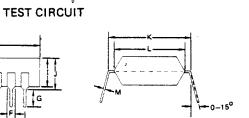

PACKAGE OUTLINE μPB8214C

| ITEM | MILLIMETERS | INCHES       |  |  |

|------|-------------|--------------|--|--|

| A    | 33 MAX.     | 1.28         |  |  |

| 8    | 2.53        | 0.1          |  |  |

| C    | 2.54        | 0.1          |  |  |

| 0    | 0.5 ± 0.1   | 0.02 ± 0.004 |  |  |

| E    | 27.94       | 1.1          |  |  |

| F    | 1.5         | 0.059        |  |  |

| G    | 3.2 MIN.    | 0.125 MIN.   |  |  |

| н    | 0.5 MIN.    | 0.02 MIN.    |  |  |

| 1    | 5.22 MAX.   | 0.205 MAX.   |  |  |

| 7    | 5.72 MAX.   | 0.225 MAX    |  |  |

| K    | 15.24       | 0.6          |  |  |

| L.   | 13.2        | 0.52         |  |  |

| М    | 0.25 ± 0.1  | 0.01 ± 0.004 |  |  |